原创

【数字IC】高级数字 IC 设计(10)Sobel 设计

Sobel算法是做图像的必备技能,其设计流程如下:

mif文件的制作→ 调用ip核生成rom以及仿真注意问题→ 灰度处理→ 均值滤波:重点是3*3 像素阵列的生成→ sobel边缘检测→ 图片的显示→ 结果展示 。

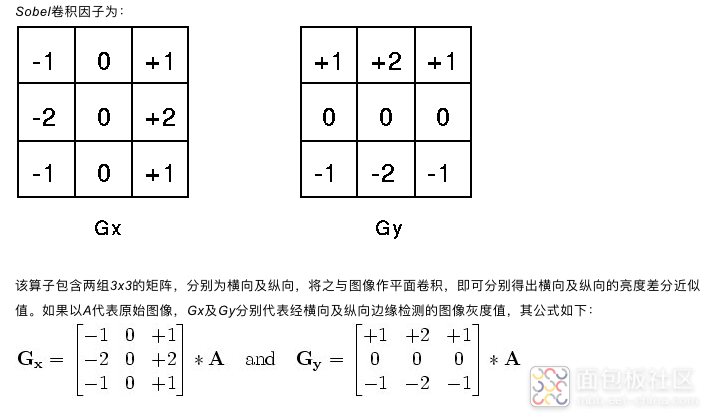

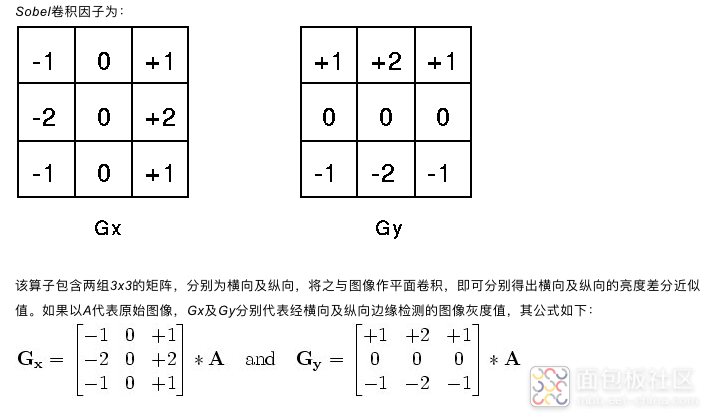

在技术上,Sobel算法是一离散性差分算子,用来运算图像亮度函数的灰度之近似值。在图像的任何一点使用此算子,将会产生对应的灰度矢量或是其法矢量。

module Sobel(</p>

clk_i,rst_n,iStart,iData,oData,data121,oStart); input clk_i;input rst_n;input [7:0] iData;input iStart; output [7:0] oData;output oStart; output [9:0] data121; //=======================================================//reg & wire//=======================================================reg [7:0] oData;wire oStart; //for Row bufferwire [7:0] Data_Row0,Data_Row1,Data_Row2; //for data121wire [9:0] data121;reg [9:0] DataV0,DataV1,DataV2; assign Data_Row0 = iData; //for odatawire [9:0] DataSub,Subina,Subinb; //for ostart delayreg [2:0] Start_delay; //=======================================================//row buffer//=======================================================Row_Buffer Row_Buffer (.clock(clk_i),.shiftin(iData),.taps9x(Data_Row2),.taps4x(Data_Row1)); //=======================================================//data121//=======================================================assign data121 = {2'd0,Data_Row0} + {1'b0,Data_Row1,1'b0}+ {2'd0,Data_Row2};always @ (posedge clk_i or negedge rst_n)beginif(!rst_n)beginDataV0 <= 10'd0;DataV1 <= 10'd0;DataV2 <= 10'd0;endelse beginDataV0 <= data121;DataV1 <= DataV0 ;DataV2 <= DataV1 ;endend //=======================================================//oData//=======================================================assign Subina = (DataV0 > DataV2) ? DataV0 : DataV2;assign Subinb = (DataV0 > DataV2) ? DataV2 : DataV0;assign DataSub = Subina - Subinb; always @ (posedge clk_i or negedge rst_n)beginif(!rst_n)beginoData <= 8'd0;endelse beginif(DataSub[9:8] == 2'd0)oData <= DataSub[7:0];elseoData <= 8'hff;endend //=======================================================//oStart whole delay will be 3//=======================================================always @ (posedge clk_i or negedge rst_n)beginif(!rst_n)beginStart_delay <= 3'd0 ;endelse beginStart_delay[0] <= iStart;Start_delay[1] <= Start_delay[0];Start_delay[2] <= Start_delay[1];endend assign oStart = Start_delay[2]; reg [9:0]Hcount;reg [8:0]Vcount; always @ (posedge clk_i or negedge rst_n)beginif(!rst_n)beginHcount <= 10'd0;Vcount <= 9'd0;endelse beginif(oStart)beginif(Hcount == 10'd639 && Vcount == 9'd479)beginHcount <= 10'd0;Vcount <= 9'd0;endelse if(Hcount == 10'd639)beginHcount <= 10'd0;Vcount <= Vcount + 1'b1;endelse beginHcount <= Hcount + 1'b1;endendelse beginHcount <= 10'd0;Vcount <= 9'd0;endendend endmodule复制代码

/4

/4

文章评论(0条评论)

登录后参与讨论