引言

当制造诸如异质结双极晶体管(HBT)的电子器件时,可控的各向异性半导体干法蚀刻工艺是非常理想的。此外,在光学逻辑门阵列中,取样光栅的曲率小到60nm,这对于获得低耦合系数是至关重要的。在众多干法蚀刻方法中,活性离子蚀刻(RIE)和电感耦合等离子体(ICP)是最常用的方法。在RIE系统中,室压往往高达100毫托或更高;相反,ICP源能够在1-20毫托的较低压力下工作。它们也可以产生比电容耦合放电高10-100倍的等离子体密度。

SiCl4基等离子体是ICP蚀刻中III-V族材料的常用放电方式。为了利用ICP方法的优点,英思特使用SiCl4/Ar在低RF功率水平下对砷化镓(GaAs)基材料进行了非常低速率的干法蚀刻研究。

实验与讨论

将100纳米的二氧化硅沉积在砷化镓(GaAs)衬底上等离子体增强化学气相沉积(PECVD),之后,用常规光刻法将样品图案化成3、5、10、20和30微米宽的条纹。接下来,用CF4等离子体进行RIE以选择性地去除二氧化硅,从而将图案从光致抗蚀剂转移到下面的二氧化硅上。去除抗蚀剂后,剩余的SiO2充当ICP蚀刻的硬掩模。

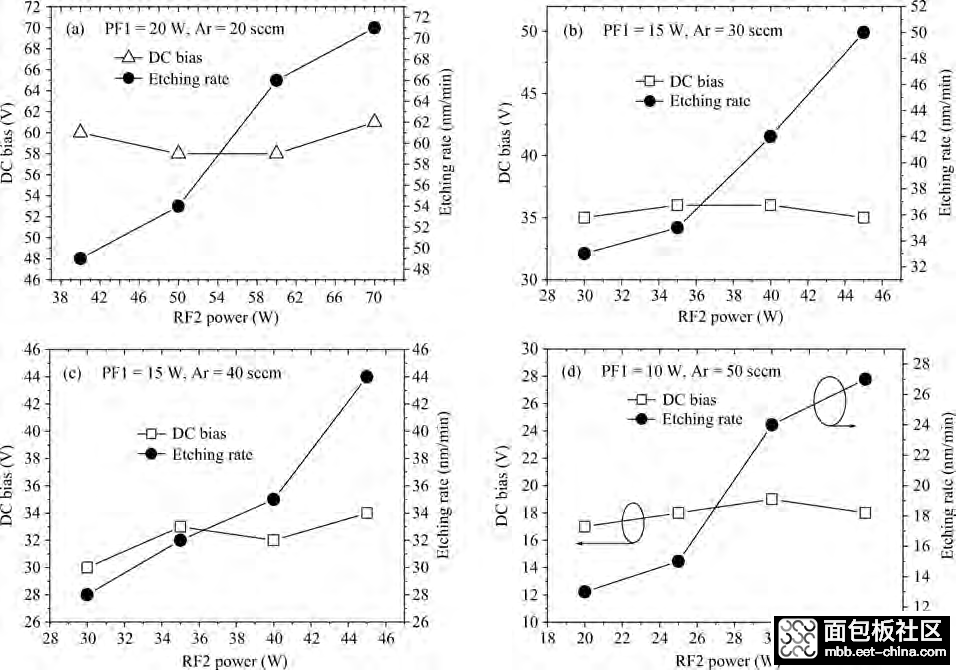

图1显示出了对于不同的Ar流速和RF1的功率水平,蚀刻速率以及DC偏置作为RF2功率的函数。DC偏置是线圈和样品之间测得的电势。低DC偏压是理想的,因为它是蚀刻损伤的量度。蚀刻时间选择为2分钟,以便用稳定的等离子体蚀刻,因为等离子体在产生的最初几秒是不稳定和复杂的。等离子体在极低的RF1功率水平下不会点燃。为了解决这个问题,英思特在较高的RF1功率下点燃等离子体,然后在5s内将其快速切换到较低的功率水平。SEM照片表明,这种方法不影响蚀刻性能。

图1:不同的RF1功率水平和Ar流量,蚀刻速率和DC偏置作为RF2功率的函数

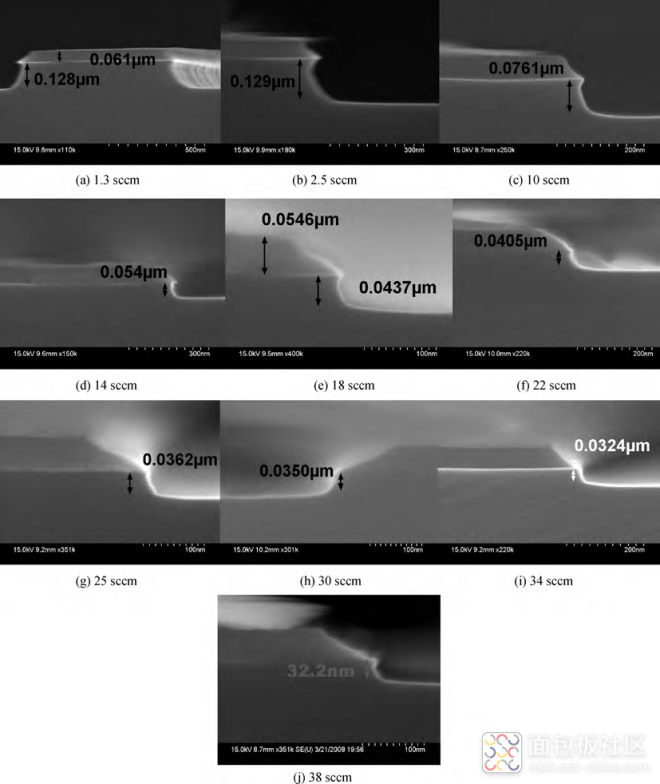

图2:低射频功率水平下不同氩气流量对蚀刻轮廓的影响

Ar在等离子蚀刻中充当缓冲气体,可以改变蚀刻轮廓、表面光滑度甚至蚀刻速率。我们将RF1功率保持在10瓦,RF2功率保持在20瓦,压力保持在1毫托,并将Ar流量从1.3 SCCM增加到50sccm。蚀刻时间固定在2分钟。SEM照片如图2所示。

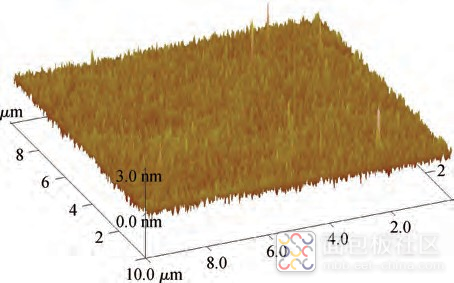

在蚀刻2分钟后,蚀刻深度为25nm,这比我们预期的要低,这是由于离子蚀刻的滞后效应导致其中半导体材料的蚀刻速率受蚀刻开口尺寸影响的。较小的开口会导致较低的蚀刻速率。图3给出了大面积蚀刻区域的3d表面形态。

在等离子体蚀刻过程中有两种蚀刻效应。一种是化学蚀刻,这可能导致底切蚀刻。另一种是物理刻蚀,通过离子轰击诱导垂直刻蚀。很明显,尽管物理碰撞产生了各向异性的蚀刻,但它会损坏蚀刻表面。

图3:蚀刻大面积区域的三维形态

结论

英思特利用SiCl4/Ar等离子体的高度可控砷化镓ICP刻蚀在射频功率水平和气体流量方面进行了研究。我们在最佳参数下获得了低至13nm/min的刻蚀速率,成功制作了深度为25nm、周期为140nm的浅砷化镓光栅。

/1

/1

文章评论(0条评论)

登录后参与讨论