ise是一个支持数字系统设计的开发平台,并且在进行设计开发时基于基于相应的器件型号,在软件设计时选择的器件型号是与实际下载板上的器件型号相同的。

二输入逻辑门设计如下图所示:

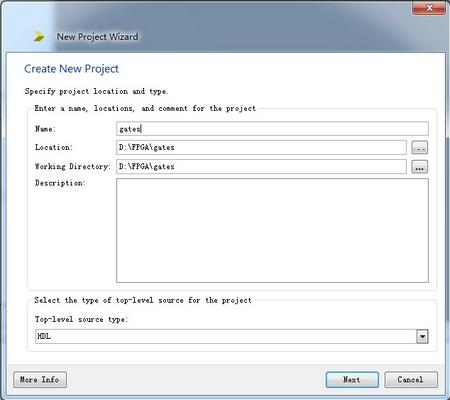

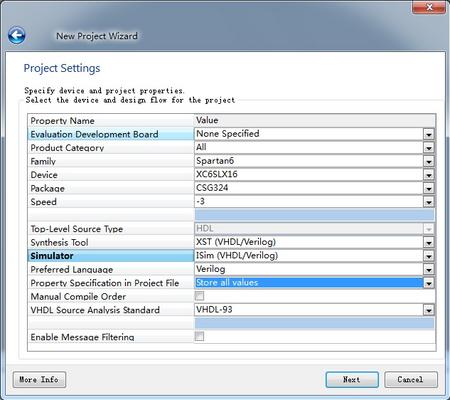

第一步,建立工程。

双击桌面该图标 ,打开ise软件(也可以从开始菜单启动),每次打开都会默认恢复上一次的工程界面,当然如果是第一次打开的话,由于没有工程记录,所以会在工程管理区是一片空白。选择File->New Project,新建一个工程,如下图:

,打开ise软件(也可以从开始菜单启动),每次打开都会默认恢复上一次的工程界面,当然如果是第一次打开的话,由于没有工程记录,所以会在工程管理区是一片空白。选择File->New Project,新建一个工程,如下图:

第二步,设计输入和代码仿真

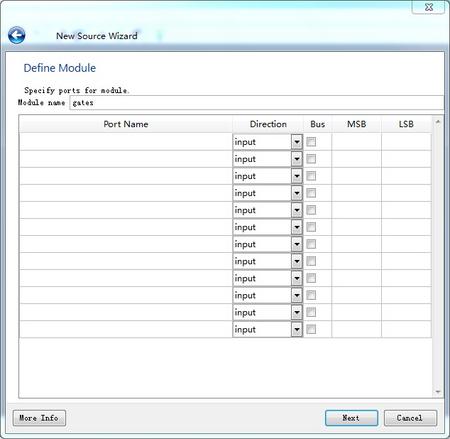

在右侧上部的工程管理区Hierarchy空白处右击->New Source,如下图所示:

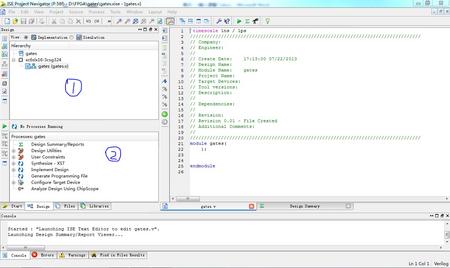

这里的界面可以不用管,当然如果写上了的话,在生成gates.v文件时,会自动生成相应的管脚的声明,这个是ise比较省力的一方面。点击Next,出现刚才设置的内容,如果没有错误,点击Finish即可。如下图:

这里的界面可以不用管,当然如果写上了的话,在生成gates.v文件时,会自动生成相应的管脚的声明,这个是ise比较省力的一方面。点击Next,出现刚才设置的内容,如果没有错误,点击Finish即可。如下图:

上图①区为工程管理区,②区为过程管理区。

在gates.v中输入2输入逻辑门的设计源码,如下:

module gates2(

input wire a,

input wire b,

output wire[5:0]z

);

assign z[5] = a&b;

assign z[4] = ~(a&b);

assign z[3] = a|b;

assign z[2] = ~(a|b);

assign z[1] = a^b;

assign z[0] = ~(a^b);

endmodule

双击过程管理区的Synthesize-XST,进行综合,如果在输入源码过程中,出现语法错误等,在综合过程中会有提示,Synthesize-XST前面会有个X,并且在信息显示去会提示警告和错误的数量,双击错误或者警告,会智能提示,当然提示不一定对。综合后如果通过,Synthesize-XST前面会显示√。

第三步,设计测试文件。

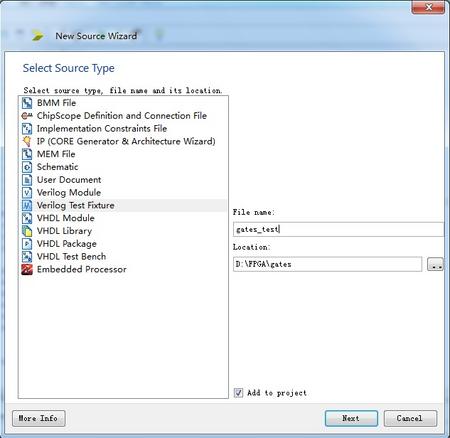

在工程管理区将View改为Simulation,并在工程管理区右击->New Source,选择Verilog Test Fixture,并填写filiname,如下图:

点击Next,选择gates文件再点击Next,检查无误后点击Finish,ise将自动生成对应的测试文件,我们的任务是在 initial begin-end中填写测试代码,代码如下:

initial begin

a <= 0;

b <= 0;

$display("a = %b,b = %b,z = %b",a,b,z);

#200

a <= 1;

b <= 0;

$display("a = %b,b = %b,z = %b",a,b,z);

#200

a <= 0;

b <= 1;

$display("a = %b,b = %b,z = %b",a,b,z);

#200

a <= 1;

b <= 1;

$display("a = %b,b = %b,z = %b",a,b,z);

end

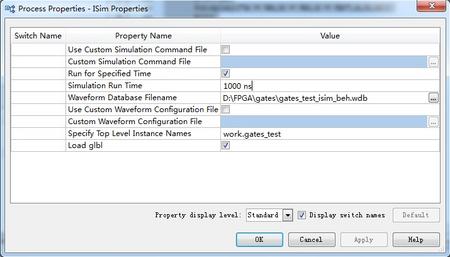

单击工程管理区中的gates_test,双击过程管理区中ISim Simulation中的Behavioral Check Syntax,进行语法检查,通过后,右击Simulate Behaviorl Model,选择Process Properties选项,对仿真进行设置,如下图:

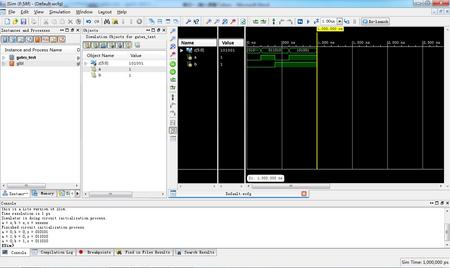

仿真时间设置为1000ns,这个根据整个测试的周期和时钟来自己确定。设置完成后点击OK,双击Simulate Behaviorl Model,ISim窗口打开,如下图:

第四步,综合与实现。

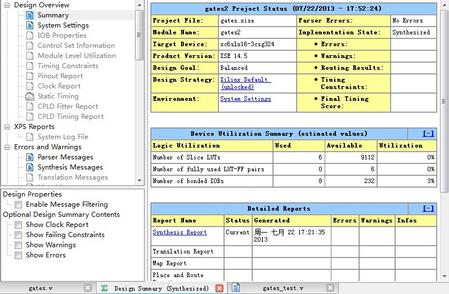

在ise的工程管理中,View改为Implementation,双击过程管理区的Synthesize-XST,将生成Design Summary,综合可能有3种结果:如果综合后完全正确,则在Synthesize-XST前面有一个打勾的小圆圈;如果有警告,则出现一个带感叹号的黄色小圆圈;如果有错误,则出现一个带叉的红色小圆圈。如果综合步骤没有语法错误,XST能够给出初步的资源消耗情况,点击Design Summary,即可查看,如下图:

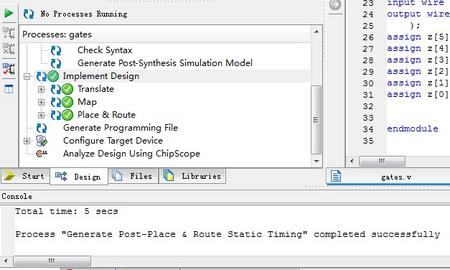

综合完成后,下一个步骤就是实现(Implementation)。所谓实现,是指将综合输出的逻辑网表翻译成所选器件的底层模块和硬件原语,将设计映射到器件结构上,进行布局布线,达到在选定器件上实现设计的目的。实现主要分为3个步骤:翻译(Translate)逻辑网表、映射(Map)到器件单元与布局布线(place & Route)。在ISE中,执行实现过程,会自动执行翻译、映射和布局布线过程:也可单独执行。在过程管理区双击Implementation Design选项,就可以自动完成实现的3个步骤,如下图所示:

第四步,硬件配置。

所谓硬件配置,就是将设计中的输入输出的一些端口映射到芯片相应的管脚上,有两种方法可以实现,一种是通过创建管脚约束文件,另一种是通过ISE自带的Ahead功能实现。

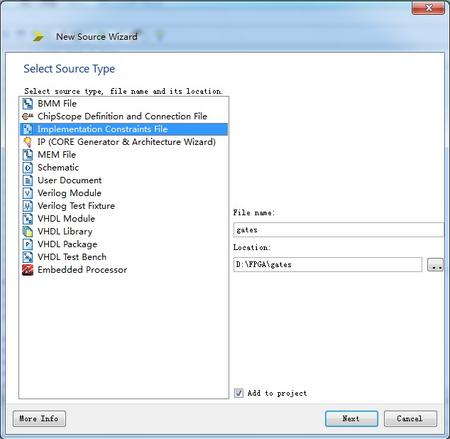

1、通过管脚约束文件实现方法:

在代码管理区中右击->New Source,创建Implement Constraints File,并命名为gates,然后点击Next->Finish,如下图:

在gates.ucf文件中输入管脚约束代码,如下:

NET "a" LOC = T5;

NET "b" LOC = V8;

NET "z[0]" LOC = T11;

NET "z[1]" LOC = R11;

NET "z[2]" LOC = N11;

NET "z[3]" LOC = M11;

NET "z[4]" LOC = V15;

NET "z[5]" LOC = U15;

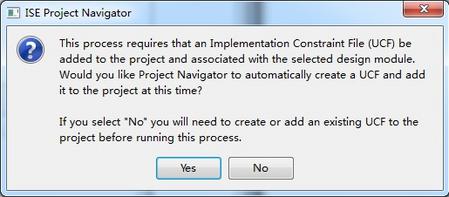

2、通过Ahead功能实现,在过程管理区中双击即可,如下图:

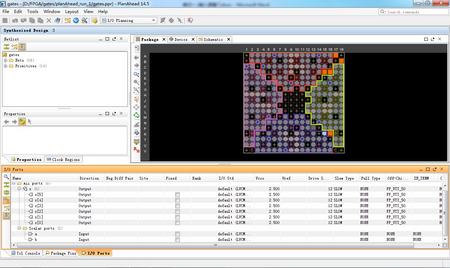

双击后会发现系统自动创建一个ucf文件,然后再次双击Post-Synthesis,即可打开该软件,如下图:

并在I/OPorts区展开管脚,添加上相应的管脚约束即可,如下图:

添加完管脚约束,在过程管理区中双击Implement Design,对设计进行实现,所谓实现,是指将综合输出的逻辑网表翻译成所选器件的底层模块和硬件原语,将设计映射到器件结构上,进行布局布线,达到在选定器件上实现设计的目的。实现主要分为3个步骤:翻译(Translate)逻辑网表、映射(Map)到器件单元与布局布线(place & Route)。在ISE中,执行实现过程,会自动执行翻译、映射和布局布线过程:也可单独执行。在过程管理区双击Implementation Design选项,就可以自动完成实现的3个步骤,如下图所示。如果设计没有经过综合,就会启动XST完成综合,在综合后完成实现过程。经过实现后能够得到精确的资源占用情况。在Design Summary即可看到具体的资源占用情况。

电子匠人 2013-9-26 16:51

用户377235 2013-9-26 13:26

电子匠人 2013-9-16 09:25

电子匠人 2013-9-15 17:06

用户1407078 2013-9-15 15:18

用户427957 2013-9-14 18:54

电子匠人 2013-9-12 18:18

用户385857 2013-9-12 15:52