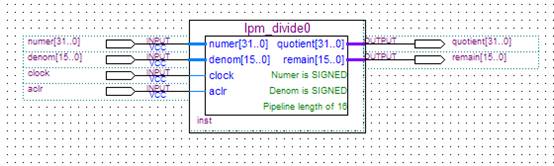

在尝试了多种优化方案后,设计的时序还未达到收敛,但我却已黔驴技穷了。冥思苦想了几天,我决定重新分析一下问题,将这段时间的优化过程回顾了一下,忽然间发现曾在《时序优化一例(一)》中分析过除法器IP的问题,查询过这IP核的性能,初步估计可能达不到250MHz,是不是这IP核本身真就不行呢?其实在《时序优化一例(三)》中已经可以验证了,因为通过分区和创建Logiclock区域将除法器与其它模块在synthesis和fitter过程中分离开来了,此时时序分析后的关键路径还停留在除法器内部,为了充分验证其性能,单独对此除法器建了个工程,顶层原理图如图1所示,其它的逻辑完全不加,并且时钟约束到250MHz。

图1

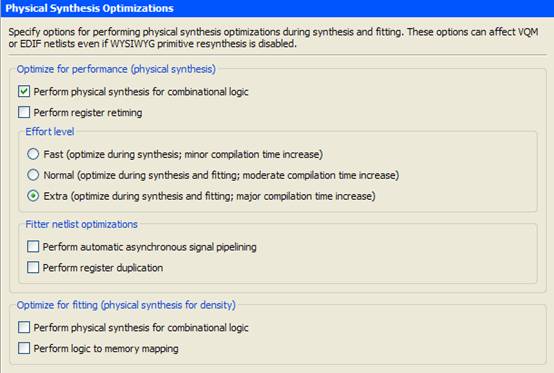

然后对此模块采用《时序优化一例(二)》中相同的物理综合优化,如图2所示,使能Perform physical synthesis for combination logic选项,并且Effort level设置成Extra

图2

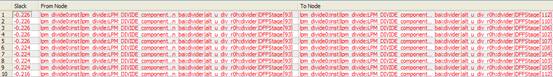

通过TimeQuest Timing Analyzer分析一下时序,果然未收敛,如图3所示,建立余量达到-0.226ns,与《时序优化一例(三)》中优化后的结果-0.224ns几乎相同,看来前面分析的正确,是除法器IP真就不行!这个问题只能通过自己重新编写除法器程序解决了,可以不采用altera官方的IP核,而此阶段的时序优化任务算是告一段落了!

图3

总结:

还是对这阶段时间时序优化的实践做一个总结吧!通过边实践边记录的方式学习,发现学习效率提高了不少,需要记录就有了解决问题的动力,在解决问题的过程中就将理论知识结合起来了,以前两个月对时序方面理论知识的学习为基础,因此可以对实践中发现的问题可以找到合理的解释。

在《时序优化一例(一)》中通过修改代码的方法优化了关键路径,效果还是很明显的,在以后的时序优化过程中,应该将此方法作为首选,因为代码是时序不理想的根源。首先需要通过时序分析工具(TimeQuest Timing Analyzer)找到关键路径,分析关键路径,可能是由于路径中逻辑过长或者节点扇出过大,然后根据关键路径修改对应的代码,可以加入流水线级或优化逻辑代码来优化时序。

在《时序优化一例(二)》中通过物理综合优化时序,在无法使用修改代码方法优化时序时,可以采用此方法。这部分优化是软件自动进行的,包括优化逻辑、优化布局布线等。

在《时序优化一例(三)》中为了分析时序问题,采用了Design Partition和Logiclock方法。其实这两个工具的主要用处就是分析,Design Partition可能主要用于增量编译;而Logiclock将逻辑的布局布线限定在一个区域中,更易于对时序路径进行分析。

通过这阶段的学习实践,巩固了时序方面的理论知识,掌握了几种时序优化的方法,当然还有许多其它方法,需要继续学习提高。

/2

/2

文章评论(0条评论)

登录后参与讨论