在使用两种方法(《时序优化一例(一)》,《时序优化一例(二)》)对设计进行时序优化后,设计的建立时间余量从-1.070优化到-0.240,但是时序还未达到收敛,继而尝试了许多其它方法:

(一)局部优化

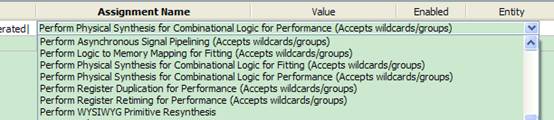

在《时序优化一例(二)》中的物理综合优化是全局的,可能对关键路径的优化还不够彻底。翻阅了一些资料,发现可以针对一个模块或者节点进行局部优化,因此可以直接对关键路径进行直接优化。方法是在QuartusII软件中,打开Assignments->Assignment Editor,如图1所示,可以在其中加入需要优化的节点或者模块,优化选项与全局优化选项类似,如图2所示,在Assignment Name下拉菜单中可选择不同的优化策略。

图1

图2

但是遗憾的是采用局部优化后,时序还是没有收敛!

(二)LogicLock

使用Logiclock可以创建一个floorplan,用于将设计中的部分模块逻辑的布局布线限制在模块区域中。但是其主要用于增量编译中,与design partition配合使用,将一个设计分区的布局布线限定在一个Logiclock区域中,如果分区的布局布线已达到要求,可以设置保留该分区布局的布局布线信息,那下次编译时可以跳过对该设计的布局布线过程,减少了编译时间。

但是使用Logiclock对时序性能并没有什么好处,反而可能会起到反效果。因为fitter并不对Logiclock区域之间的布线进行优化,而如果Logiclock区域划分不合理,关键路径正好处于跨区域中,那在之前对关键路径所作的时序优化算是白费了。

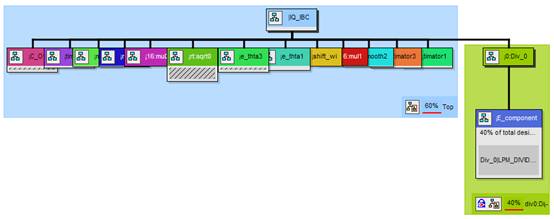

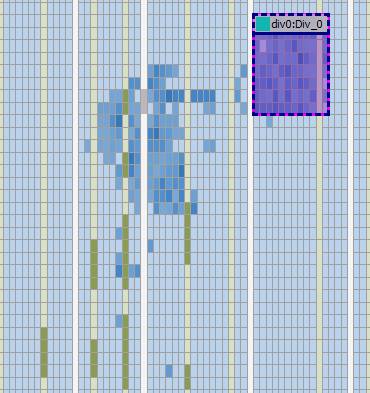

在我的设计中,现阶段关键路径处于除法器IP内部,也没别的什么办法去优化这个IP了,可能是其它模块的布局布线对除法器模块产生了影响,那就“瞎猫碰死耗子”一把,试一试,万一有小惊喜呢!使用Logiclock将除法器布局布线与其它模块的布局布线隔离,将此除法器模块单独建立分区和创建Logiclock区域。分区如图3所示,可以看到Div模块因为分区被单独分离出来;Logiclock如图4所示,div模块的逻辑被限定在单独的一个Logiclock区域中布局布线。

图3

图4

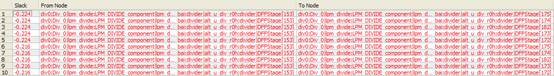

然后来check一下timing,值得欣慰的是,时序好了一些,如图5所示,建立时间余量减小到-0.224ns了,关键路径还在除法器内部。通过分区逻辑隔离、创建Logiclock区域进行布局布线隔离还是起到了意想不到的效果,尽管这效果很小。

图5

/5

/5

用户377235 2014-5-6 22:57

用户424077 2013-2-26 11:01