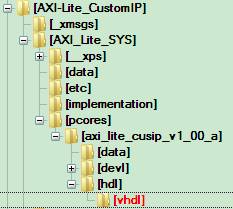

图3-8 自定义IP路径

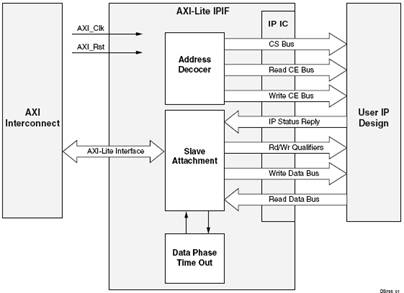

自定义IP设计完后,需要为其编写功能代码,在如图3-8路径中,有一个vhdl文件夹,自定义IP设计生成的HDL代码默认是由VHDL编写的。 其中有两个文件:axi_lite_cusip.vhd和user_logic.vhd,如图3-9所示为AXI-Lite IP接口信号图,其中文件axi_lite_cusip.vhd实现AXI-Lite IPIF模块的功能,文件user_logic.vhd实现User IP Design模块的功能,因此自定义IP的功能代码主要在user_logic.vhd文件中编写。此处的设计Xilinx就比Altera更人性化了, 在Altera的NiosII自定义外设设计时,类似axi_lite_cusip.vhd和user_logic.vhd的接口文件都需要工程师自己编 写,而Xilinx相当于为工程师提供了一个模板,只需要添加相应的功能代码就可完成设计,这样大大减少了工作量,工作效率得到提高。

图3-9 AXI-Lite IP接口信号图

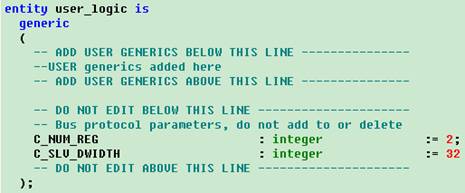

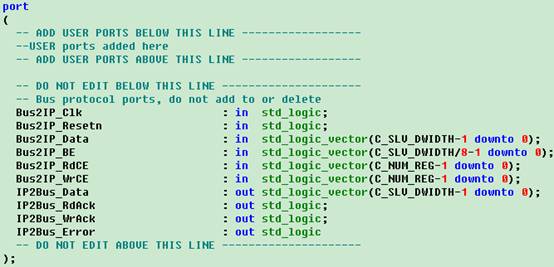

下面来看一下user_logic.vhd里面有什么奥秘,如图3-10所示为模块参数,其中参数C_NUM_REG表示寄存器的数量,在本设计中 设置了两个,一个用于读取DIP拨码开关状态值,另一个用于控制LED灯;如图3-11所示为模块接口信号,其中BUS2IP_**表示从AXI- Lite总线输入到IP的信号,包含时钟信号BUS2IP_CLK、复位信号BUS2IP_Resetn、数据信号Bus2IP_Data、字节使能信号 Bus2IP_BE、读使能信号Bus2IP_RdCE、写使能信号Bus2IP_WrCE;而IP2BUS_**表示从IP输出给AXI-Lite总线 的信号,包含数据信号IP2Bus_Data、读确认信号IP2Bus_RdAck、写确认信号IP2Bus_WrAck、错误确认信号 IP2Bus_Error。

图3-10模块参数

图3-11 模块接口信号

功能模块需要加入的功能为两部分,对应两个寄存器,如表1所示为两个寄存器的映射。

表1 两寄存器映射

|

寄存器 |

使能信号 |

对应地址映射 |

功能 |

|

reg0 |

BUS2IP_RdCE=“10” |

C_BASEADDR |

只读 |

|

reg1 |

BUS2IP_WrCE=“01” |

C_BASEADDR+0x4 |

只写 |

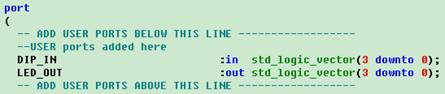

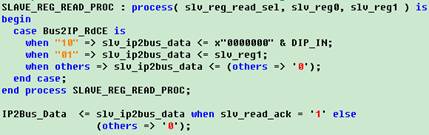

reg0是读取DIP拨码开关状态值功能,因此是一个读寄存器操作,首先需要加入DIP拨码开关的输入端口,如图3-12所示,相关功能代码如图3-13所示。

图3-12 加入端口

图3-13 读操作功能代码

reg1是控制LED灯输出功能,因此是一个写寄存器操作,加入的LED输出端口如图3-12所示,相关功能代码如图3-14所示。

图3-14 写操作功能代码

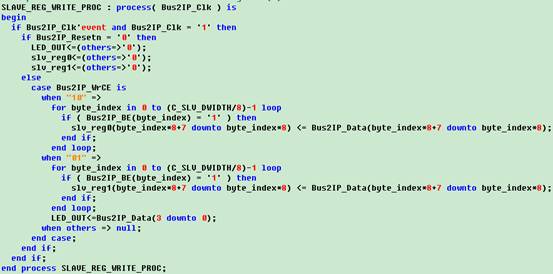

功能代码编写完成后,将AXI_LITE_CUSIP加入到系统中,如图3-15所示,自定义的IP是连接到AXI-Lite总线上的。

图3-15 AXI_LITE_CUSIP总线连接

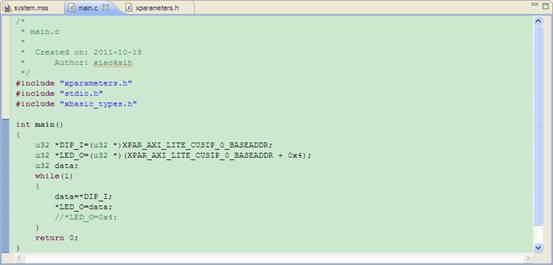

系统建立完成后,在ISE中进行编译生成比特流文件,然后在SDK软件中编写相应软件代码,代码如图3-16所示,主要实现功能是读取DIP状态 值,然后将读取得到的DIP状态值通过LED输出,其中读取DIP状态值通过读取reg0得到,reg0的地址为 XPAR_AXI_LITE_CUSIP_0_BASEADDR;而控制LED输出通过写reg1得到,reg1的地址为 XPAR_AXI_LITE_CUSIP_0_BASEADDR + 0x4。

图3-16 SDK软件代码

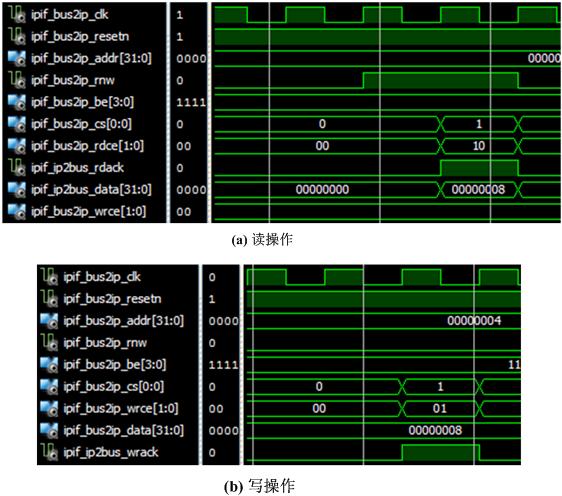

一切就绪之后,通过ISIM仿真,查看自定义IP工作状态,如图3-17(a)所示为读操作,当 bus2ip_rnw=’1’,bus2ip_rdce=”10”时,表示AXI-Lite总线请求一次读操作,而自定义IP将ip2bus_rdack 置’1’,将数据赋值给ip2bus_data应答这次读操作;如图3-17(b)所示为写操作,当 bus2ip_rnw=’0’,bus2ip_wrce=”01”时表示AXI-Lite总线请求一次写操作,而自定义IP将ip2bus_wrack 置’1’,并读取数据应答这次写操作。

图3-17

本节主要介绍了基于AXI-Lite总线的自定义IP的设计,其中详细介绍了自定义IP的设计流程。从最后仿真图可以验证自定义IP,基本完成了读和写操作。详细的设计流程和基于开发板调试的实际效果可观看设计视频,视频链接如下:

PC端设计调试:http://v.youku.com/v_show/id_XMzE0MzA1Nzc2.html

上板实际效果:http://v.youku.com/v_show/id_XMzE0Mjk1MjE2.html

Hoki 2012-9-30 17:02

Hoki 2012-9-30 17:01

用户377235 2012-9-26 23:30

还有就是,应该用什么工具修改IP代码并进行综合,是XPS吗?您的博客中说:“ 功能代码编写完成后,将AXI_LITE_CUSIP加入到系统中”,但是中间的步骤省略了,我修改完了代码,加入LED和按键,并修改了Port Map,结果加入到XPS中后并没有看到LED和按键的Port

用户412852 2012-9-26 17:57

Hoki 2012-9-20 15:52

用户412852 2012-9-18 18:01

用户162746 2008-10-20 08:38