这一节主要讲解一下转置型FIR滤波器实现。

FIR滤波器的单位冲激响应h(n)可以表示为如下式:

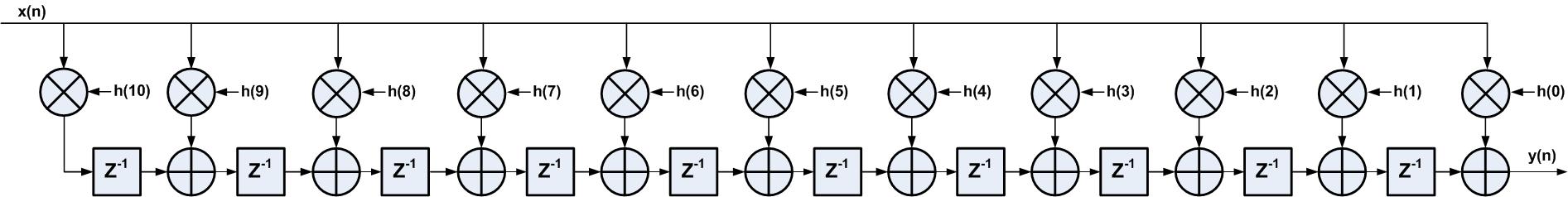

对应转置型结构的FIR滤波器,如图1所示,抽头系数与上一节中讲解直接型FIR滤波器的实例相同,滤波器阶数为10。

图1

可以发现转置型结构不对输入数据寄存,而是对乘累加后的结果寄存,这样关键路径上只有1个乘法和1个加法操作,相比于直接型结构,延时缩短了不少。

综合得到结果如下:

Number of Slice Registers: 1

Number of Slice LUTs: 18

Number of DSP48E1s: 11

Minimum period: 4.854ns{1} (Maximum frequency: 206.016MHz)

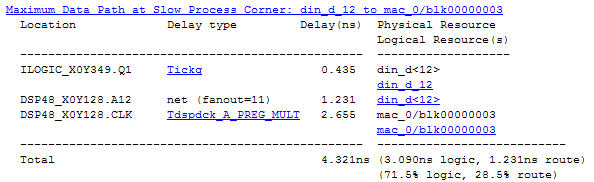

关键路径延时报告如图2所示,其中乘累加操作延时Tdspdck_A_PREG_MULT 2.655ns;另外还有一项net delay居然有1.231ns,如此大是因为fanout=11,仔细研究可以发现在h(n)表达式中x(n)与所有11个抽头系数进行了乘法操作,因此fanout达到了11,这也是转置型FIR滤波器的缺点:输入数据的fanout过大。

图2

线性相位:

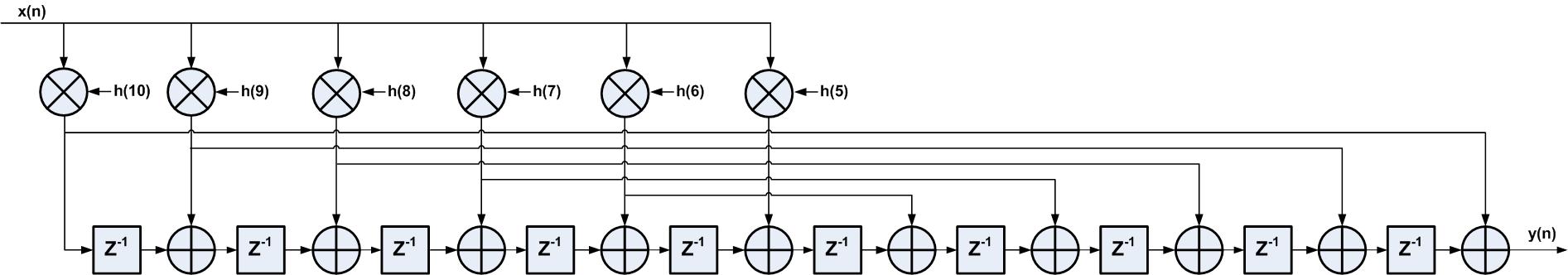

与直接型结构相同,由FIR滤波器的线性相位特征,转置型结构的FIR滤波器也可优化,如图3所示为线性相位FIR滤波器转置型结构,总共11个抽头系数,其中5对系数两两相同,因此可以省去5个乘法器,采用6个DSP资源实现转置型FIR滤波器。

图3

流水线实现:

为了进一步缩短关键路径的延时,将乘法器和加法器逻辑分割开,中间加入流水线级,结果如图4所示,在线性相位结构的基础上,加入一级寄存器,这样最大限度上优化时序。

图4

综合得到结果如下:

Number of Slice Registers: 355

Number of Slice LUTs: 340

Number of DSP48E1s: 6

Minimum period: 3.861ns{1} (Maximum frequency: 259.000MHz)

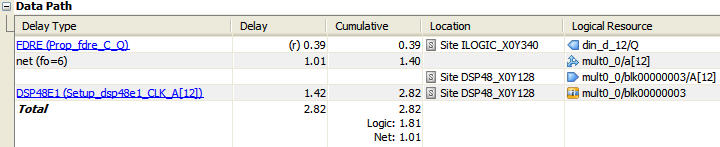

如图5所示为与图2中相对应路径的延时报告(图2由ISE的Timing Analysis工具产生,图5是由PlanAhead的Timing Analysis工具产生),其中由于采用线性相位结构,输入信号的fanout只有6,延时从原先的1.231ns减小到1.01ns;并且分隔乘法器和加法器逻辑之后,关键路径上只有乘法器的延时:1.42ns。

图5

相关代码(见附件):

转置型:fir_transpose

线性相位流水线实现:fir_transpose_lin

/3

/3

用户430619 2013-3-9 15:08