随着FPGA的广泛应用,所含的资源也越来越丰富,从基本的逻辑单元、DSP资源和RAM块,甚至CPU硬核都能集成在一块芯片中。在做FPGA设计时,如果针对FPGA中资源进行HDL代码编写,对设计的资源利用和时序都有益。下面主要讲解一下如何巧用FPGA中资源:

1. 移位寄存器

FPGA中的移位寄存器使用在前面的博文中有所论述,Xilinx FPGA中的LUT可以作为SRL使用,主要可参考此博文《Xilinx 7系列FPGA使用之CLB探索》,在此想补充论述一下SRL的延时,首先看一下如下代码,实现了一个19级的移位寄存器。

module srl_test(

input clk,

input rst,

input din,

output dout

);

reg din_d;

always@(posedge clk) begin

if(rst)

din_d<=1'b0;

else

din_d<=din;

end

reg [18:0] d_sh;

always@(posedge clk) begin

d_sh<={d_sh[17:0],din_d};

end

assign dout=d_sh[18];

endmodule

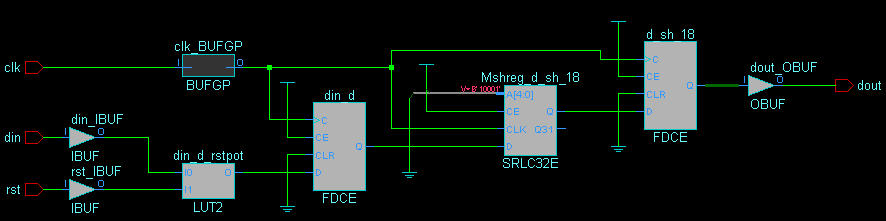

综合得到结构如图1所示,其中输入din由FF(din_d)寄存,随后的移位操作由一个SRL32E和FF组成,SRL中A=“10001”,实现了18级移位,因此SRL32E和FF的组合也能实现19级的移位,但是代码中dout是直接assign组合输出,并没有输出寄存,为什么综合得到结构是FF寄存输出,以下分析一下原因。

图1

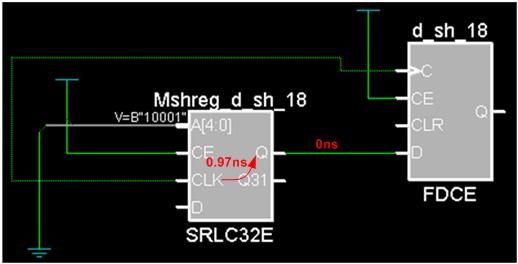

在FPGA内部时序分析一般以register-to-register为基础模型,首先来看一下图2所示路径,为srl32-to-ff的路径,其数据路径延时报告如图3所示,延时Prop_srlc32e_CLK_Q表示充当移位寄存器的LUT的clk_to_out延时,达到0.97ns,相比于FF的clk_to_out延时(0.24ns)相差甚大,如果没有最后一级的FF寄存,则输出为纯组合逻辑输出,这段路径的延时将会被引入到下一级模块的时序分析中,下一级模块的输入如果也没有输入寄存,则这一段数据路径的延时将会很大,不利于时序收敛;而加入FF寄存,直接切断了数据路径,在这段register-to-register模型中,数据路径延时仅有LUT的clk_to_out延时0.97ns,在一般情况下都能达到时序收敛。因此综合器自动将最后一级移位以FF形式实现,在代码功能不变的前提下,优化了时序;而且这个FF是同一个Slice中的FF,并不会消耗多余的Slice,由于SRL32E和FF处于同一个Slice,它们之间的走线属于内部走线,因此延时将会很小,由延时报告中SRL32E到FF(d_sh_18)的走线延时为0ns可以验证。

图2

图3

移位寄存器综合得到的SRL+FF组合结构体现了综合器的智能,但是此结构仅限于静态地址的移位寄存器实现,动态地址的移位寄存器的Q端是直接组合逻辑输出的,需要人为地在代码中添加FF寄存。

2. Register大搜索

在FPGA中的register资源可以说是无处不在,几乎每个角落都有它的身影,Xilinx 7系列FPGA中,每个Slice中有8个register,除此之外,在DSP48E1、Block RAM蕴藏了很多register,其中在1个DSP48E1中多达上百个。

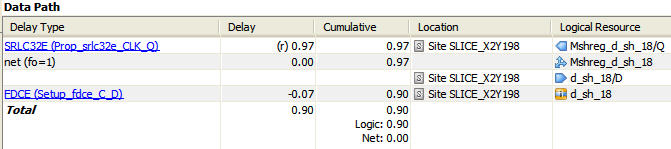

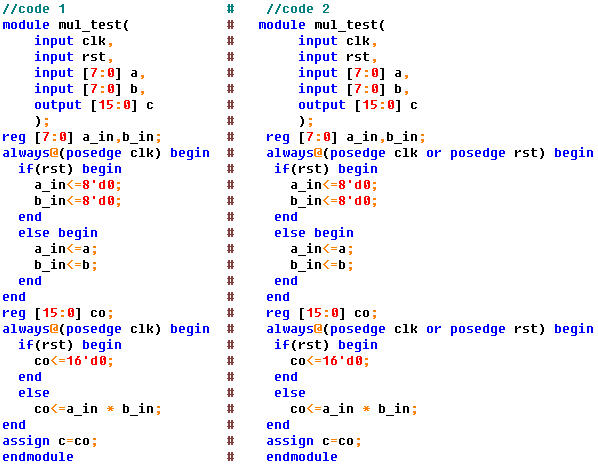

首先讲解一下如何使用DSP48E1中丰富的register资源,如下两段代码:

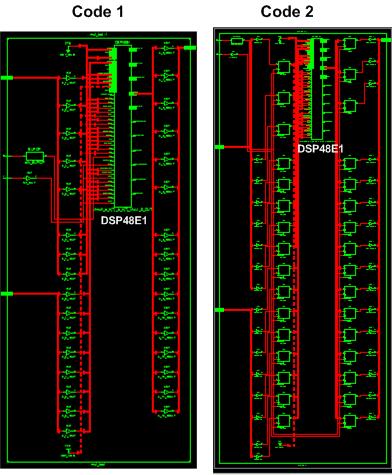

综合得到资源利用和性能对比如下表所示,结构如图4所示,其中Code1和Code2都使用了1个DSP48E1资源;Slice Resigter,Code2使用比Code1多了32个,用于输入2*8-bit和输出16-bit信号的寄存,而Code1没有使用额外的Slice的register资源,是因为这些register是在DSP48E1中实现了;并且Code2的Fmax相比于Code1也较差,是因为Code2中结构使用了额外的Slice Resigter,连接乘法器需要外部走线,增加了数据路径延时,而Code1中register与乘法器之间是内部走线,延时可以忽略,因此时序上较好。

|

|

Code 1 |

Code 2 |

|

Slice Registers |

0 |

32 |

|

DSP48E1s |

1 |

1 |

|

Maximum frequency |

360.750MHz |

253.678MHz |

图4

而比较Code1和Code2的差异,就是复位,Code1中寄存采用的是同步复位,而Code2采用异步复位,因为DSP28E1中的register只支持同步复位,如果采用异步复位,综合器就不会采用DSP48E1中的register实现,而是使用额外的Slice Resgiter,因此建议在使用DSP资源时采用同步复位,这样可以充分使用其中的register资源,对于FPGA资源耗用和性能上都有益。

而使用Block RAM中register资源与DSP类似,复位方式也需要是同步综合器才能识别。

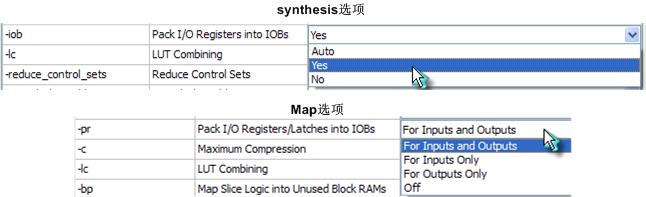

另外还有一处的register可供利用,那就是IOB,通过设置synthesis和map选项,可以将输入和输出的register映射到IOB中的register实现,如图5为选项设置,在synthesis选项中,将-iob设置为Auto或者Yes,在Map选项中,将-pr设置为For Inputs and Outputs。

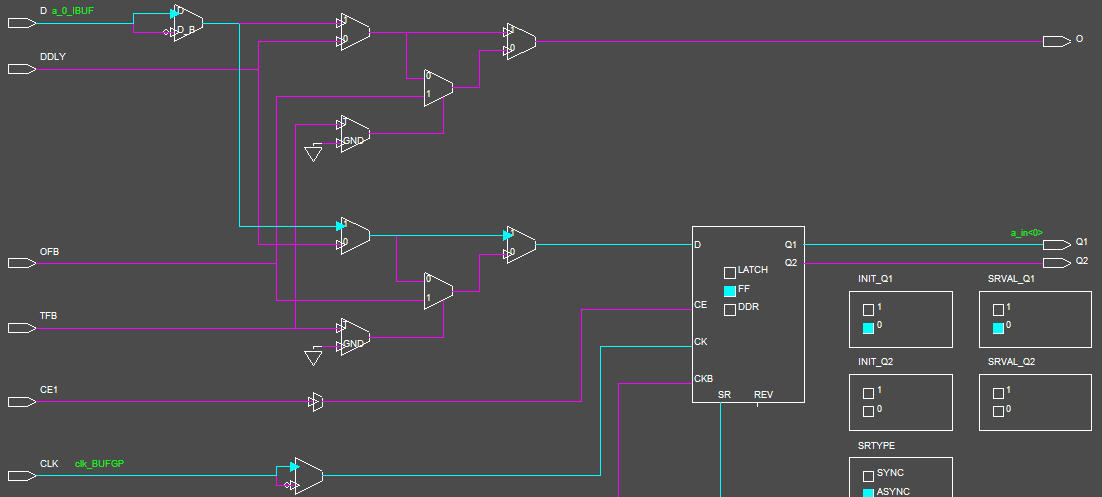

对上述Code2进行综合实现,得到报告如下,报告显示输入和输出register并没有使用额外的Slice Resigter实现,而是映射到了IOB Flip Flops中,如图6所示为IOB中的register。

Slice Logic Utilization:

Number of Slice Registers: 0 out of 407,600 0%

Number of Slice LUTs: 0 out of 203,800 0%

IO Utilization:

Number of bonded IOBs: 34 out of 500 6%

IOB Flip Flops: 32

图6

综上,在做FPGA设计时,可以充分利用DSP、Block RAM、IOB等资源中的register,不但节省资源而且可以在一定程度上提高性能。

/3

/3

用户4677 2012-6-25 11:55