这一节评测LX9开发板的核心SPARTAN6系列FPGA芯片XC6SLX9,对其内部结构做一个深层次探究。

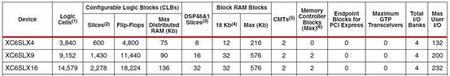

表1中列出了XC6SLX9芯片所含的资源情况,其中几项主要的资源Slices 1430个、DSP48A1 16个、Block RAM 18Kb 32个和I/O 200个。在公司用习惯了K7这种大型器件,看到LX9的资源列表我表示很无语,这么少资源能干啥。但是看着LX9开发板上的跑马灯一闪一闪的,貌似正非常鄙视地回复我:别看我资源少,照样能嵌microblaze、照样能控制Ethernet、照样能…

表1

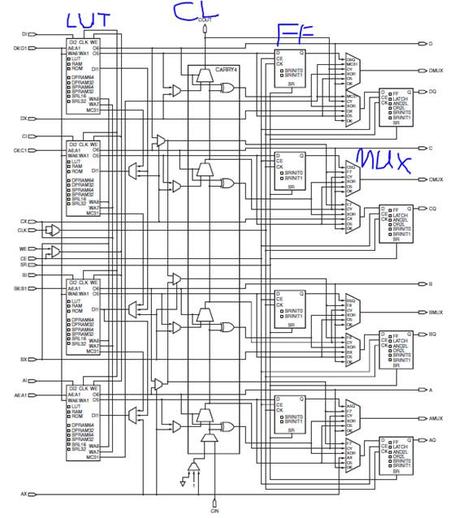

好了,废话不多说,开始探秘XC6SLX9,首先从她的Slice开始,Slice是XC6SLX9逻辑资源的基本组成单元,一个CLB(Configutable Logic Block)中包含2个Slice。而Slice又分为2种:SLICEL和SCLICEM,其中SCLICEM比较特殊,不仅可充当普通的逻辑资源,而且可实现分布式RAM或者移位寄存器,当FPGA设计中需要少量RAM,即可采用SLICEM实现。

Slice:基本结构如图1所示,是由4个6输入LUT、进位链carry logic、8个Flip Flop和复选器multiplexer组成。而SLICEM中主要是LUT比较特殊,可以充当RAM,每个LUT是6输入的,可以实现一个64 bit的RAM,因此一个SLICEM 4个LUT最大可实现256 bit RAM

图1

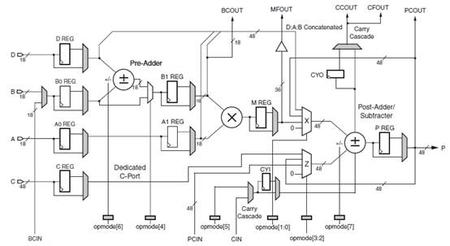

DSP48A1:基本结构如图2所示,这个乘法器硬核可实现如(B±D)x A±C操作,包含利于滤波的预加器pre-adder,并且最大支持18bit x 18bit的乘法操作。DSP48A1是数字信号处理的利器,可惜在XC6SLX9里太少了。

图2

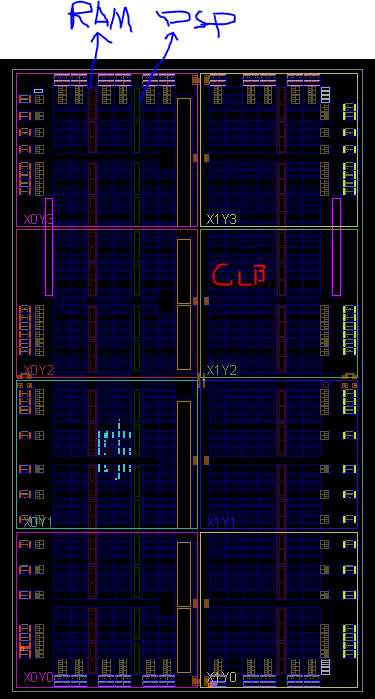

Block RAM:在需要大量数据存储时,可以选择Block RAM资源,每块为18Kb大小,因此哪怕只用了1bit也占用了1个Block RAM资源。

如图2所示为XC6SLX9的内部结构图,其中红色竖条块为Block RAM,绿色竖条块为DSP48A1,其它大部分为Slice资源,整个芯片资源分布非常整齐。

图3

/5

/5

文章评论(0条评论)

登录后参与讨论