时钟对于FPGA就像我们的心脏,时刻控制着“跳动”的频率以及“血液”的流速;时钟域好比通过心脏的血液血型,不同血型的血液会产生排斥作用。在设计中建议时钟越少越好,好比于人有两个甚至更多的心脏,其内脏工作将会多么混乱。但是某些情况下多时钟又不可避免,比如从FPGA外部输入的数据,其自带有个随路时钟,数据终归要在FPGA内部时钟域下处理,这来自外部的“血液”如何处理才能与内部的“血液”融合呢?配对及转换工作则是必不可少的,这就引入本节的主题:跨时钟域处理(Clock Domain Crossing):

跨时钟域处理需要两方面的工作:1. 设计者处理;2. FPGA工具(Vivado)处理。

1. 设计者处理

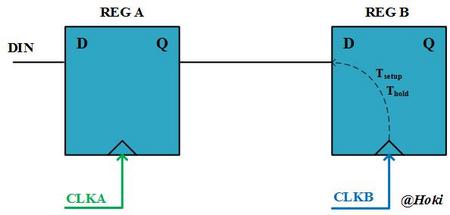

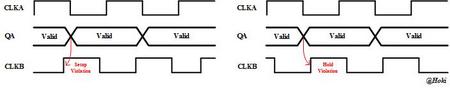

首先讲解一下如果不进行跨时钟域处理,会出现什么问题呢?如图1所示路径,QA属于CLKA时钟域的数据输出,另一个时钟CLKB去捕获节点REG A的输出QA,假定CLKA与CLKB是异步时钟,它们之间的相位并不固定,因此捕获过程中可能会出现建立冲突(setup violation)和保持冲突(hold violation),如图2所示,左右分别为发生建立冲突和保持冲突的情况。

图1

图2

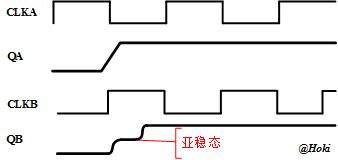

当冲突出现时(我感觉整个人都不好了),会发生什么事情呢?在发生建立冲突或者保持冲突,捕获节点(REG B)会处于一个不定的状态,正常的状态是高电平或者低电平,而此时的状态停留在高电平和低电平的中间,无效的电平X,称这个状态为亚稳态。如图3所示,捕获节点输出保持在亚稳态,可能在整个时钟周期内都保持在亚稳态,由于不正确的状态,其后连接的逻辑在功能实现上就会出现问题,比如一个判断信号上升沿的逻辑,通常判断D == HIGH && D_PREV == LOW(D为信号当前电平状态,D_PREV为信号上个时钟的电平状态)是否成立,而发生亚稳态时则D_PREV == X,这个上升沿将会错过。因此,加入跨时钟域处理设计是必须的。

图3

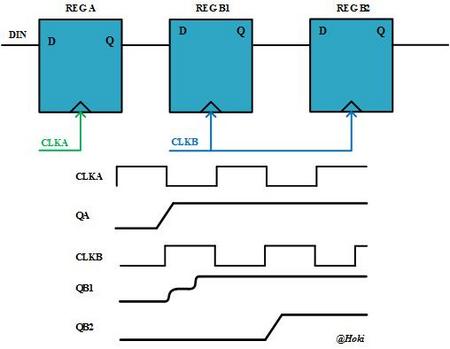

对于单比特信号的跨时钟域处理,常用的方法是“打两拍”,即在捕获时钟域中加入两个寄存器进行时钟转换,如图4所示,加入REG B1和REG B2,虽然REG B1处于亚稳态状态,但是REG B2的输出QB2能稳定在正常的电平上,由于REG B1和REG B2之间没有多余的逻辑,REG B1能有充裕的时间稳定状态,此情况下REG B2能完美地隐藏REG B1的亚稳态。在捕获时钟的频率比较高的情况下,如果一个REG B2还未能隐藏亚稳态,拍数也可以增加三个或者更多,当然一般情况下,两拍足矣。

图4

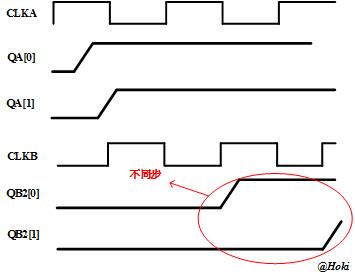

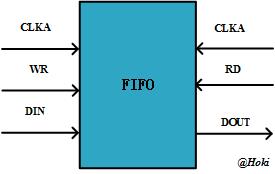

对于多比特总线数据的跨时钟域处理,能否也使用“打两拍”的方法呢?答案见图5,虽然REG B2的输出是稳定的,稳定在哪一个电平是不确定的,不过会在当前时钟或者下一个时钟输出正确电平,即偏差在一个时钟周期,也就是说不能保证所有比特位的状态一致,也是这个原因,导致传输多比特总线数据时各比特位不同步,常用的解决方法是加入FIFO隔离,如图6所示,FIFO能有效地隔离两个时钟域,避免亚稳态的发生。

图5

图6

2. FPGA工具(Vivado)处理

Vivado采用XDC对时序进行约束,默认情况下,会分析所有时钟的路径,当然也包括跨时钟域的路径。

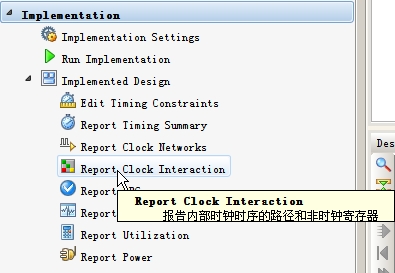

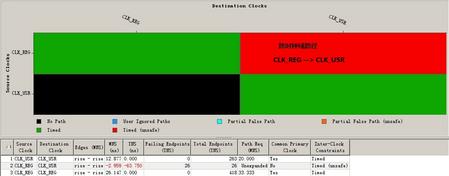

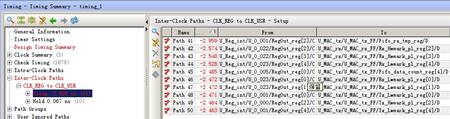

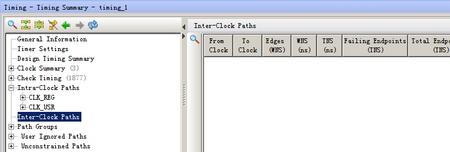

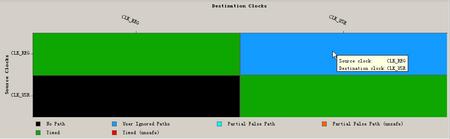

设计经过综合实现后,在Implementation中点击Report Clock Interaction(见图7),得到设计中所有时钟的交互情况,如图8所示,共有两个时钟:CLK_REG和CLK_USR,红色区域表示Timed(unsafe),说明两个时钟间有时序路径。

图7

图8

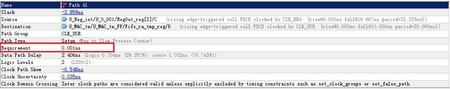

可以发现在图8底部时序分析的结果,有红色报警说明有路径时序未收敛,打开时序分析报告(见图9),source clock是CLK_REG,destination clock是CLK_USR,说明是一条跨时钟域路径,其中Requirement只有0.001ns,显然对跨时钟域路径的分析不合理,因此通常在保证设计者处理完成后,添加时序约束,是Vivado忽略对跨时钟域路径进行时序分析。

图9

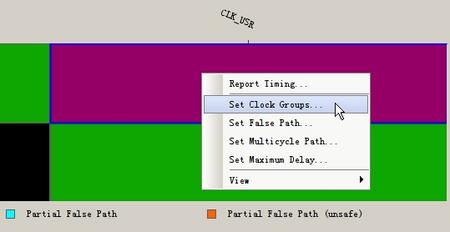

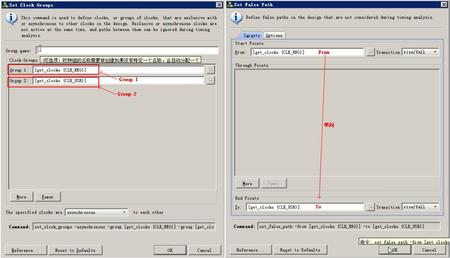

可以通过设置时钟组(clock group)或者设置假路径(false path)处理跨时钟域路径。如图10所示,在clock interaction中红色区域右击,选择Set Clock Groups或者Set False Path,

图10

Set Clock Group和Set False Path的区别是,前者设置了双向(CLKA-TO-CLKB和CLKB-TO-CLKA)的路径,而后者只设置单向(CLKA-TO-CLKB或者CLKB-TO-CLKA)的路径,此例中因为只有单向区域有路径交互,因此使用Set False Path即可。

图11

添加完约束后,时序报告中Inter-Clock Paths没显示有路径,并且没有未收敛的时序路径,如图12所示,Clock Interaction中原先红色区域变成了蓝色(User Ignored Paths),可以确认约束生效。

图12

/5

/5

用户377235 2016-1-21 10:37

用户1739383 2014-6-22 18:50