Vivado软件相比于ISE的一大转变就是约束文件,ISE软件支持的是UCF(User Constraints File),而Vivado软件转换到了XDC(Xilinx Design Constraints)。XDC主要基于SDC(Synopsys Design Constraints)标准,另外集成了Xilinx的一些约束标准,可以说这一转变是Xilinx向业界标准的靠拢。Altera从TimeQuest开始就一直使用SDC标准,这一改变,相信对于很多工程师来说是好事,两个平台之间的转换会更加容易些。首先看一下业界标准SDC的原文介绍:

Synopsys' widely-used design constraints format, known as SDC, describes the "design intent" and surrounding constraints for synthesis, clocking, timing, power, test and environmental and operating conditions. SDC has been in use and evolving for more than 20 years, making it the most popular and proven format for describing design constraints. Essentially all synthesized designs use SDC and numerous EDA companies have translators that can read and process SDC.

Xilinx原先的自成一派(UCF)其实其实也算做的不错,相信使用过UCF的工程师也有同感,并没有什么不便。像Apple那样软件和硬件都自成一派而且能与其它所有派别抗衡的,背后需要有多强大的团队支持,可能Xilinx可是考虑到这点,不想花费过多的精力去维护。(个人见解)

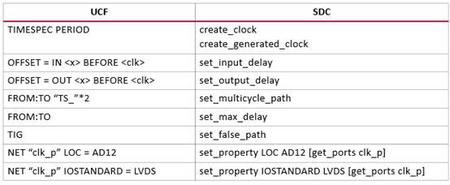

文归正题,如果有读者以前没有使用XDC/SDC的经验,这边讲解一下如何从UCF到XDC的转换。如图1所示为UCF与SDC的约束命令比较,可以发现常用的命令都能对应上。

图1

下面简单举例说明:

Clock Period:

UCF :NET "clka" TNM_NET = "clka";

TIMESPEC "TS_clka" = PERIOD "clka" 13.330 ns HIGH 50.00%;

XDC :create_clock -name clka -period 13.330 -waveform {0 6.665} [get_ports clka]

Input Port:

UCF :OFFSET = IN 8 BEFORE clka;

XDC :set_input_delay -clock clka 2 [all_inputs]

注: clock period = 10 ns.

Output Port:

UCF :OFFSET = OUT 12 AFTER clkc;

XDC :set_output_delay -clock clkc 8 [all_outputs]

注:clock period = 20 ns.

除了以上约束命令的差别外,UCF和XDC间的主要差别如下:

1. XDC是顺序执行约束,个约束指令有优先级

2. UCF一般约束nets对象,而XDC约束类型是pins, ports和cells对象

3. UCF约束默认不对异步时钟间路径进行时序分析,而XDC约束默认所有时钟是相关的,会分析所有路径,可以通过设置时钟组(set_clock_groups)取消时钟间的相关性

下面介绍一下在Vivado中添加XDC文件以及加入约束命令的方法:

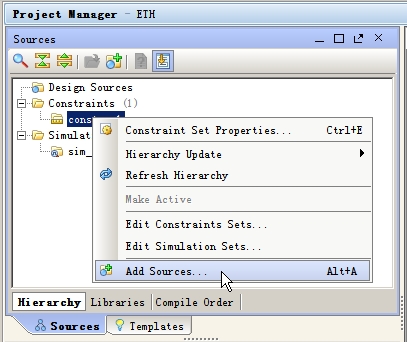

首先在Project Manager中展开Constraints类,选择Add Sources即可添加或者新建XDC约束文件,如图2所示。

图2

选择新建的XDC文件,双击打开,选择左侧的Templates,其中有XDC约束命令的实例,所有的约束命令都可以在其中找到,非常方便,如图3,4所示。

图3

图4

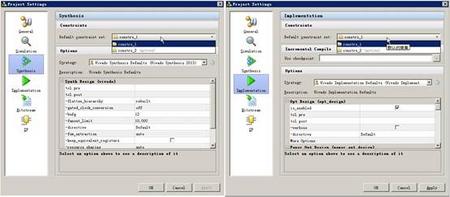

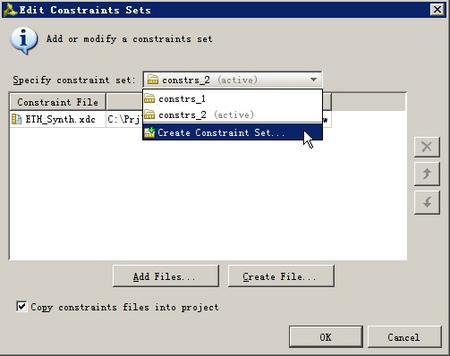

XDC约束文件可以在编译综合和实现过程中使用时,在综合和实现设置中都能选择需要的约束,如图5。通过创建约束文件集,如图6,设计者可以使能不同的约束集合测试FPGA设计的性能;在约束文件集中可以包含多个XDC约束文件,在FPGA设计比较复杂时,可以分模块或者IP核约束,相应的则有多个XDC约束文件,这样设计和维护效率都能得到提高。

图5

图6

/5

/5

用户1803330 2014-11-24 09:09

用户1749120 2014-4-22 19:59

用户377235 2014-3-21 14:02