在深入讲解XDC约束前,先介绍一下基本的时序约束、分析的概念。

Timing Path:

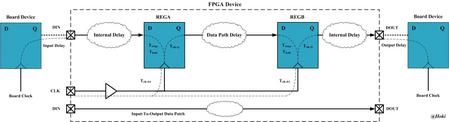

图1中包含了主要的时序分析路径:

1. 输入端口到FPGA内部时序单元的路径

2. FPGA内部时序单元间的路径

3. FPGA内部时序单元到输出端口的路径

4. 输入端口到输出端口的路径

图1

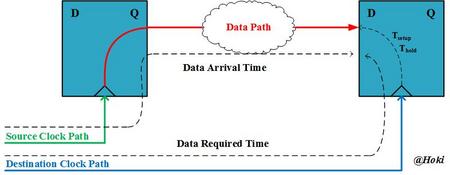

不管时序单元是在FPGA内部还是外部,除了第4条路径,它是从输入端口到输出端口,其间没有锁存,其它3条路径的时序分析都以2个时序单元间的路劲进行分析,如图2所示。

第一个时序单元上的时钟称为source clock(启动时钟),第二个时序单元上的时钟称为destination clock (锁存时钟),时序分析从source clock的上升沿开始,到之后的destination clock的上升沿结束,时序分析的过程就是检验数据在两个上升沿时间差内经过数据路径传输后是否满足要求,数据到达时需要满足后一级时序单元的setup/hold要求,其本质上是需要数据在到达后一级时序单元时不发生亚稳态,数据能够被稳定地采集到并且稳定地输出。

图2

Clock Setup Check:

检验Setup是否满足要求,这边引入setup slack概念,只要setup slack的值大于零即Setup检查满足要求,其计算公式如下:

以下是代码片段:

以下是代码片段:

以下是代码片段:

setup slack = (destination clock edge time - source edge time) + (destination clock path delay - source clock path delay) - clock uncertainty - setup time - clock to output time - data path delay

= Tdestination_to_source + (Tclk-D2 – Tclk-D1) – Tclk_uncertainty – Tsetup – uTco - Tdata_path_delay

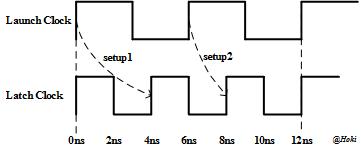

其中第一部分Tdestination_to_source,当source clock和destination clock为异步时钟时,如图3中实例,source clock的周期等于6ns,destination clock的周期等于4ns,首先假定2个时钟的相位差为0,图中在这种情况下有2个setup关系,setup1下Tdestination_to_source = 4ns,setup2下Tdestination_to_source = 2ns,在实际分析中应该选取最严格的情况,即选取setup2这种。

图3

而当source clock和destination clock为同一个时钟时,Tdestination_to_source的值很显然就是时钟周期Tclk_period,这也是时序分析最多的情况了,进一步推导setup slack = Tclk_period+ (Tclk-D2 – Tclk-D1) – Tclk_uncertainty - Tsetup – Tdata_path_delay > 0,可以得到:

Tclk_period > Tclk_uncertainty + Tsetup + Tdata_path_delay - (Tclk-D2 – Tclk-D1)

Tclk_period、Tclk_uncertainty可以通过时序约束确定其值,uTco, Tsetup是时序单元的属性值,(Tclk-D2 – Tclk-D1)在布局布线后其值也能确定,剩下Tdata_path_delay对Tclk_period影响最大,一个设计Setup检查中的关键路径往往是Tdata_path_delay值最大的一条路径,影响其值有很多原因,如逻辑级数过多,扇出导致布线延时过大…

Clock Hold Check:

对应Hold检查,也有hold slack,其计算公式如下:

| 以下是代码片段: hold slack = data arrival time – data required time |

以下是代码片段:

以下是代码片段:

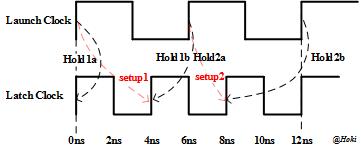

在Setup检查中,Tdestination_to_source的值选取destination clock和source clock相差最小的情况下进行分析;而Hold检查中Tsource_to_destination的值选取所有Setup关系分别进行分析,每一种Setup关系对应有两种情况,然后选取所有情况中Tdestination_to_source值大的计算对应的Tsource_to_destination

a. 取Setup关系的前一个destination clock沿,如图4中Hold1a和Hold2a

b. 取Setup关系的destination clock沿,如图4中Hold1b和Hold2b

图4

根据图4中实例计算得到:

Hold1a:Tdestination_to_source = 0ns

Hold1b:Tdestination_to_source = -2ns

Hold2a:Tdestination_to_source = -2ns

Hold2b:Tdestination_to_source = -4ns

显然选取Hold1a,对应Tsource_to_destination值为0ns

当source clock和destination clock为同一个时钟时,可以计算得到Tsource_to_destination值为0ns,进一步推导hold slack = Tsource_to_destination + (Tclk-D1 – Tclk-D2) – Tclk_uncertainty – Thold + Tdata_path_delay > 0可以得到:

Tdata_path_delay > Tclk_uncertainty + Thold + (Tclk-D2 – Tclk-D1)

由上得出数据路径的延时也不能过短,与Setup检查是矛盾对立的存在;在FPGA设计或者数字前端开发时,工程师考虑最多的是Setup是否满足要求,而Hold检查的工作主要交给工具或者负责数字后端的工程师解决。

Timing Report in Vivado:

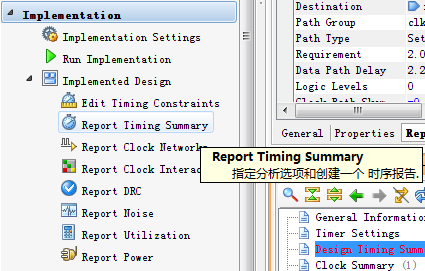

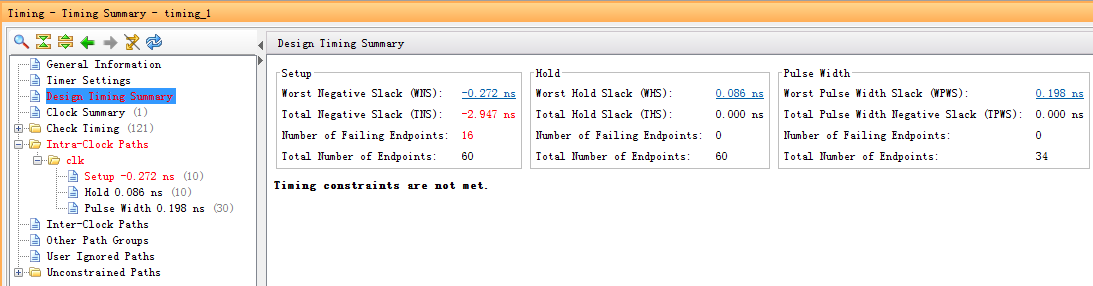

下面通过简单的实例说明一下vivado中的时序分析,当FPGA设计经过综合实现后,通过Report Timing Summary打开时序报告,如图5、6所示。

图5

图6

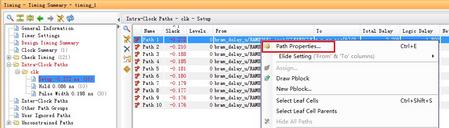

图中有红色部分表示设计中有时序不满足要求,此例中是Setup。选择Setup中未满足要求的Path,打开Path Properties,如图7所示。

图7

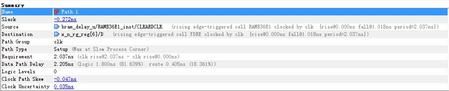

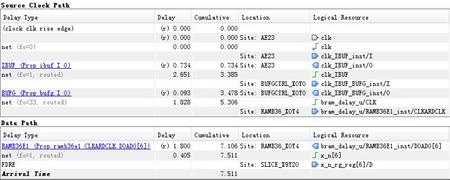

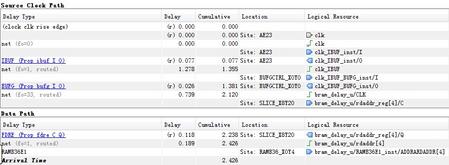

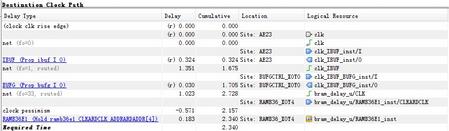

Setup关键路径的时序报告如图8所示,报告由四部分组成:Summary, Source Clock Path, Data Path和Destination Clock Path,其中由Source Clock Path和Data Path得出Arrival Time,由Destination Clock Path得出Required Time。

图8

Hold检查的报告也类似,如图9所示。

图9

/5

/5

文章评论(0条评论)

登录后参与讨论