在FPGA设计中,并不是所有的路径都需要做时序分析,称之为假路径(false path),比如有些路径在正常工作时并没有实现具体的逻辑功能,或者一些测试阶段使用的逻辑;有些是不需要做时序分析,如跨时钟域路径。

可以通过添加false_path约束,告知vivado在时序分析时忽略这些路径,这样带来的好处有:

1. 减少编译时间:vivado不需要对这些路径进行时序分析,也不需要为了优化这些路径而在P&R中花过多的时间;

2. 增加结果可靠性:约束false path并不是让vivado**,而是在实际工作中确实并不需要考虑这些路径。如果不约束,反而会使vivado偏离了正规,在努力优化false path时可能忽略了true path的时序问题。

set_false_path约束命令如下,可以约束两个节点(node_list)间的路径,也可以约束两个时钟间的所有路径:

set_false_path [-setup] [-hold] [-from <node_list>] [-to <node_list/clock>] [-through <node_list/clock>]

注:false path约束和multicycle path约束同属于时序例外(timing exception)的范畴,两者的区别是:false path约束彻底取消对该路径的时序分析,而multicycle path约束只是放松时序分析的要求,vivado依然会对multicycle path进行时序分析和优化。

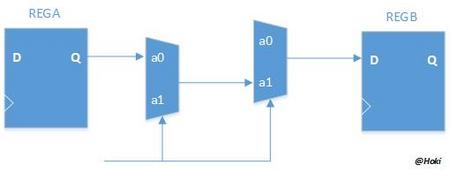

set_false_path可以直接对两节点进行约束,如图1所示路径,由于两个数据选择器由同一个信号控制,数据流分别连接了两个数据选择器的a0端和a1端,因此不可能有数据通过,可对REGA和REGB间的路径做false path约束,命令如下:

set_false_path -from {REGA} -to {REGB}

图1

另外set_false_path也可以直接对两时钟进行约束,表示将所有两个时钟间的路径都设置成false path,如下所示:

set_false_path -from [get_clocks CLKA] -to [get_clocks CLKB]

之前关于时钟约束的博文中有介绍,对两异步时钟需要设置不同的时钟组,可以通过set_clock_group约束,如下命令所示

set_clock_groups -group CLKA -group CLKB

set_false_path约束异步时钟和set_clock_group约束能达到相同的功能,不同的是set_clock_group同时约束了CLKAàCLKB和CLKBàCLKA的路径;而set_false_path是单向的,如上例中只约束了CLKAàCLKB的路径,如下两条命令就与set_clock_group等价了:

set_false_path -from [get_clocks CLKA] -to [get_clocks CLKB]

set_false_path -from [get_clocks CLKB] -to [get_clocks CLKA]

/1

/1

文章评论(0条评论)

登录后参与讨论