在Altera FPGA里面的SOPC学习过程中,软件编程中遇到的第一个编程,往往是LED灯的控制,这几天断断续续的学习了些,总算了入了NIOS II 学习的门槛,开始我对FPG**上系统的探索。在软件编程中,往往会碰到一下三个头文件,正所谓“工欲善其事必先利其器”嘛,好好理解头文件的内容, 对了解NIOS ii开发环境和代码设计是大有裨益的。借此,也是督促自己持之以恒的坚持自己的学习道路把!

——小记

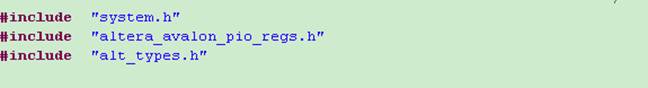

三个头文件

1、系统硬件信息的宏定义文件 System.h

1) 存放位置:

所建工程\software\工程名.syslib\Debug\system_description

2) 该文件是在第一次编译IDE开发环境的时候,编译工具根据SOPC Builder生成的目标硬件系统文件(.ptf)和系统库的配置设置生成的头文件。

System.h头文件是系统硬件信息的宏定义文件,在软件编程过程中设备的基地址就是从这个头文件中读取的。

LED_PIO_FREQ:表示Avalon总线的频率 80MH

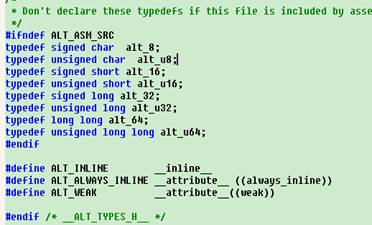

2、NIOS II相关的数据类型的宏定义文件 alt_types.h

1) 存放位置 \altera\70\nios2eds\components\altera_nios2\HAL\inc

2) HAL使用该文件头文件定义一套支持ANSI C类型的数据类型,分别定义了有符号的8、16、32、64位整数,无符号的8、16、32、64位整数

3、PIO内核寄存器相关文件 altera_avalon_pio_regs.h

1)存放位置:

\altera\70\ip\sopc_builder_ip\altera_avalon_pio\inc)

PIO内核的altera_avalon_pio_regs.h 为硬件寄存级访问文件,定义了内核寄存器以及相关访问设备的宏定义。

1) 数据寄存器

IOADDR_ALTERA_AVALON_PIO_DATA(base) PIO内核数据寄存器(基地址)

IORD_ALTERA_AVALON_PIO_DATA(base) 读访问:读入输入引脚的逻辑电平

IOWR_ALTERA_AVALON_PIO_DATA(base, data) 写访问:向PIO输出口写入新值

2)方向寄存器(在设置为双向的时候,才能操作该寄存器)

IOADDR_ALTERA_AVALON_PIO_DIRECTION(base) PIO内核方向寄存器(基地址)

IORD_ALTERA_AVALON_PIO_DIRECTION(base)

IOWR_ALTERA_AVALON_PIO_DIRECTION(base, data)

3) 中断屏蔽寄存器(输入)

IOADDR_ALTERA_AVALON_PIO_IRQ_MASK(base) PIO内核中断屏蔽寄存器

IORD_ALTERA_AVALON_PIO_IRQ_MASK(base) 读取PIO内核中断屏蔽寄存器内容

IOWR_ALTERA_AVALON_PIO_IRQ_MASK(base, data)

写PIO内核中断屏蔽寄存器内容, data为向中断断屏蔽寄存器写入数据

4)边沿捕获寄存器

IOADDR_ALTERA_AVALON_PIO_EDGE_CAP(base) 边沿捕获寄存器

IORD_ALTERA_AVALON_PIO_EDGE_CAP(base)

IOWR_ALTERA_AVALON_PIO_EDGE_CAP(base, data)

写任意值到该寄存器将使得寄存器所有位清0

/4

/4

文章评论(0条评论)

登录后参与讨论