在quartus中直接调用modelsim进行如见仿真,经过设置可以一步进行仿真。缺点是在进行仿真时,编译时间很长,优缺点也优缺点嘛。

一下是我再我的电脑中进行modelsim仿真进行设置,

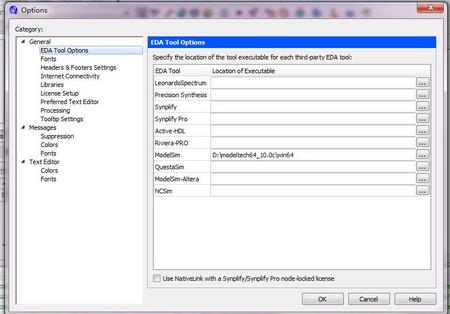

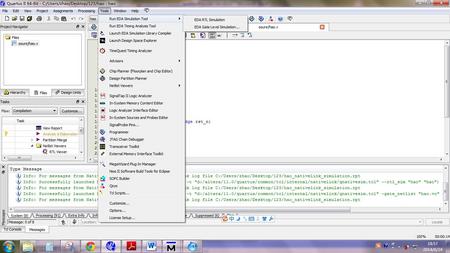

首先设置modelsim的路径。在tool菜单下点击option出现下面的对话框,在general中找打EDA tool option.因为我用的modelsim所以设置modelsim的路径(根据自己仿真软件设置)。

编写testbench文件,放到在工程文件下simulation/modelsim

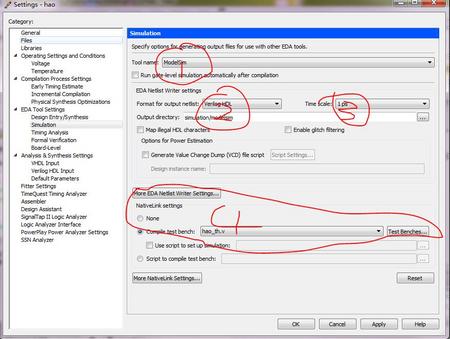

开启modelsim仿真,点击setting找到EDA Tool setting中的simulation,如下

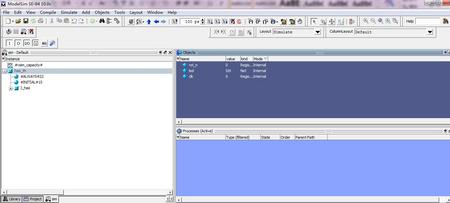

在1中选择仿真工具modelsim,在2出选择仿真语言verilog,3处仿真精度1ps,在4处点击testbenches出现下图。

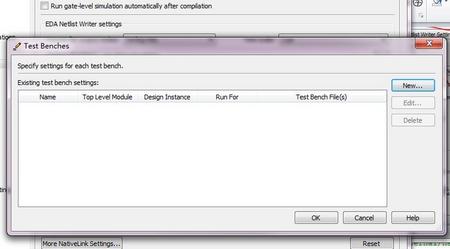

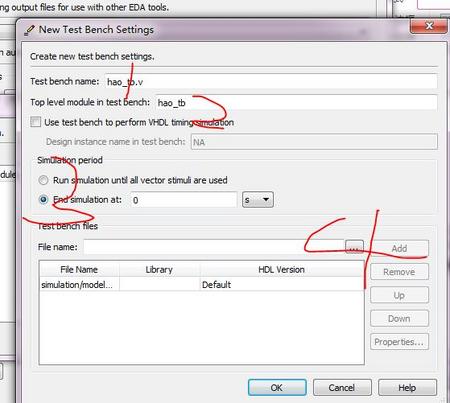

点击new,出现下图,在1处写上testbench文件名,在2处写上testbench的顶层模块名称,在3处是关于仿真时间的设置,我设置0(在modelsim中自己写入命令run 时间)。在4处事增加testbench文件名,点击…选择文件,点击add,点击ok。

完成设置了,可以进行仿真。首先编译自己文件确保文件的正确性,然后进行仿真

点击上图中的tool->run eda simulation tool->eda rtl simulation 或eda gate level

Simulation,这两个不同之处是一个是在寄存器级别仿真(即源文件),一个是经过quartus中的编译仿真。点击过后,调用modelsim仿真,

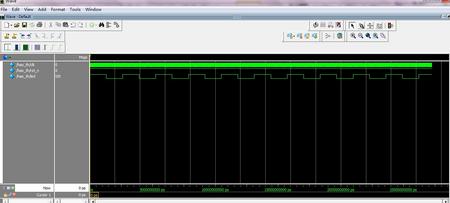

在modelsim中添加自己想要观测信号,设置信号的属性。在modelsim中的命令窗口输入运行时间(run 1000ms),波形图如下

ps:参考了黑金的 verilog那些事时序篇

/5

/5

文章评论(0条评论)

登录后参与讨论