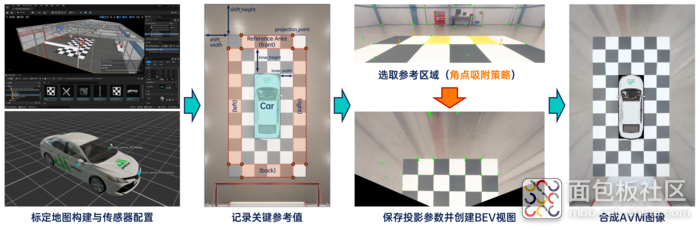

一、引言 随着自动驾驶技术的逐步落地, 感知系统对数据的依赖 正以前所未有的速度增长。 传统实车采集 虽然真实可信,但在 效率 、 安全性 、 标注精度 以及 边缘场景覆盖 方面均存在 显著限制 。 合成数据(Synthetic Data) 因具备低成本、高可控性、无限扩展性和高精度标签等优势,已成为 感知算法训练与验证 的重要数据来源。尤其在多模态、多场景、大规模自动化生成等方面, 仿真平台 正成为构建感知数据体系的重要工具。 在感知系统的开发过程中,我们依托仿真平台生成覆盖多种场景和传感器类型的合成数据,用于支持 AVM(环视系统) 开发,同时也利用合成数据生成符合公开格式标准的数据集,助力算法在 真实部署前 实现高效迭代与验证。 本文将系统介绍利用合成数据开发的具体应用流程和实践效果。 二、 AVM系统开发中的仿真验证应用 环视系统(AVM, Around View Monitor) 是自动驾驶和高级辅助驾驶系统(ADAS)中常见的功能模块,通常由4个或更多广角鱼眼相机构成,通过拼接多个摄像头图像生成车辆周围360°的鸟瞰图。 自动泊车系统(APA) 需要环视图像提供对车辆周围环境的精准感知。通过仿真方式模拟鱼眼相机布设和 BEV 拼接,可生成多种泊车场景下的高保真图像,包括地库、斜列车位、窄通道等复杂工况。 相比实车采集,仿真 不仅可以批量构造极端和边缘泊车条件,还能自动提供精确的障碍物位置与车辆姿态标注,大幅加速感知模型的训练和验证流程, 减少实车调试时间 。 传统 AVM 系统的相机 标定依赖人工操作和实车设备, 流程繁琐且精度受限 。 通过仿真 ,可控制各摄像头位置与视角,并生成可重复、可验证的图像和标定数据,适用于整车项目开发初期的快速迭代。 虚拟标定 不仅 提高了标定效率 ,还支持在方案切换、批量测试、相机布局验证等场景中自动生成对齐标注,降低人力投入, 提升系统上线速度 。 在实际开发中,AVM对图像畸变建模、拼接精度、投影映射等有较高要求,传统方法依赖人工标定与测试,周期长、灵活性差。而基于aiSim的仿真流程,可有效提升开发效率与验证精度。 通过合成数据仿真平台,我们借助从 环境搭建 到 数据生成 的 全流程仿真 ,成功实现了 4个鱼眼相机生成AVM合成数据的优化和验证。 图1 基于aiSim构建AVM图像流程 1、标定地图与仿真环境构建 我们在 Unreal Engine环境 中快速搭建6米×11米标定区域,使用2×2黑白相间标定板构成特征纹理区域,并精确布设车辆初始位置,确保视野重叠区域满足投影需求,并通过特定插件将其无缝导入仿真器中。 图2 基于aiSim插件的Unreal Engine地图编辑 2、鱼眼相机配置与参数设置 设置 前、后、左、右 四个鱼眼相机,分别具备: (1)高水平FOV(约180°); (2)不同俯仰角(前15°、后25°、侧向40°); (3)安装位置贴近真实车辆安装场景(如后视镜下方)。 我们采用了仿真器内置的 OpenCV标准内参 建模,输出图像同步生成物体的2D/3D边界框与语义标签。 图3 环视OpenCV鱼眼相机传感器配置 3、BEV图像生成与AVM拼接 利用已知相机内参和标定区域结构,通过OpenCV完成图像去畸变与投影矩阵求解,逐方向生成 BEV视图(Bird's Eye View) 。结合车辆图层与坐标对齐规则,拼接生成完整的AVM图像。 支持配置图像分辨率(如1cm²/像素)与投影视野范围,确保几何准确性。 图4 投影区域及BEV转化示意图 4、多场景合成与传感器布局优化 通过 批量仿真脚本 ,可 快速测试 不同环境(如夜间、窄巷、地库)、不同相机布局组合对AVM系统效果的影响。在算法不变的前提下,系统性评估外参配置的优劣,为传感器部署提供数据支持。 图5 不同场景下的AVM合成数据 三、合成数据构建多模态数据集 随着智能驾驶逐步从基础辅助走向复杂场景下的高阶功能,对 感知系统的数据需求 也在迅速升级。不仅需要覆盖高速、城区、出入口等典型 NOA 场景,还要求在 不同模态之间实现精确对齐 ,以支撑融合感知模型的训练与验证。在这类任务中, 仿真生成的合成数据 具备可控性强、标签精准、格式标准的优势,正在成为算法开发的重要支撑手段。 在 智能领航辅助(NOA)场景 中,系统需识别高速匝道、变道车辆、道路边缘等要素,对 训练数据多样性与标注精度要求极高。通过仿真构建 城市快速路、高速公路等 多类 NOA 场景 ,配合光照、天气、车流密度等变量自动生成图像与多模态同步数据。 这类合成数据 可用于训练检测、分割、追踪等模型模块,特别适合用于 填补实车采集难以覆盖的复杂或高风险场景 ,增强模型鲁棒性。 融合感知模型 依赖相机、毫米波雷达、激光雷达等 多种传感器协同输入 ,对数据的同步性和一致性要求较高。 通过仿真 ,可以 同时生成这三类传感器 的视角数据,并自动对齐时间戳、坐标系和标注信息,输出包括 3D 边界框、语义分割、目标速度等在内的完整标签,且格式兼容 nuScenes 等主流标准。这类数据可用于 训练融合模型识别道路上的异形障碍物 ,例如夜间难以通过视觉识别的散落杂物,或需要多模态补强感知的边缘目标。仿真带来的高度可控性也 便于统一测试条件 ,对模型性能进行定量分析与精细化调优。 在实际项目中, 合成数据的价值 不仅体现在生成效率和标注精度,更在于其 能否与下游算法开发流程无缝衔接 。为了实现这一目标,我们将 aiSim 导出的多模态原始数据,通过 自研数据处理脚本 ,转换为 基本符合 nuScenes 标准格式的数据集 。 数据构建流程如下: 1、编写符合 nuScenes 规范的传感器配置文件 首先 ,我们 根据 nuScenes 的数据结构要求 ,定义并生成了包含相机、雷达、激光雷达等传感器的配置文件,包括传感器类型、安装位置、外参信息等。该步骤确保生成数据可直接映射至 nuScenes 的 calibrated_sensor.json 和 sensor.json。 图6 激光雷达部分的传感器配置文件 图7 符合nuScenes格式的传感器配置 2、利用 aiSim Stepped 模式导出对齐的原始数据 其次,在仿真阶段, 我们启用了 仿真器的 Stepped Simulation 模式 ,该模式支持以固定时间步长(如每 0.1 秒)推进仿真,并确保所有传感器在 同一时间戳输出数据 。这种方式实现了多模态数据的时间戳全局对齐,满足 nuScenes 对数据同步的要求。 图8 aiSim相机传感器Bounding Box真值输出 然后,在仿真运行中 ,我们导出包含图像、点云、雷达、Ego Pose、2D/3D 标注等原始数据,场景长度约为 20 秒,覆盖了一段在高流量城市交通中经过十字路口的场景,作为构建示例数据集的基础。 3、结构化转换为 nuScenes JSON 格式 此外,使用 自研转换脚本 ,我们将导出的原始数据组织并填充为 nuScenes 所需的各类 JSON 文件 ,并和官方标准格式对齐,包括: scene.json:记录场景序列; sample.json:定义帧级时间结构; sample_data.json:图像、雷达、点云等数据路径与时间戳; calibrated_sensor.json 和 sensor.json:传感器类型及配置; ego_pose.json:车辆轨迹; sample_annotation.json:3D 边界框、类别、属性; instance.json、category.json、visibility.json 等其他语义层级数据。 图9 nuScenes 标准数据集JSON结构表 4、数据集结构搭建完成 最终, 构建完成的数据集具备 完整的时空同步结构 与 语义标签 ,可直接用于视觉感知、雷达检测、融合感知等模型训练与评估任务。该流程验证了合成数据向标准训练数据的转换路径,并具备可扩展性, 适用于更大规模的批量数据生成 。 图10 激光雷达点云 + 相机融合标注框 图11 激光雷达点云 + 同类型标注框 (俯视/侧视) 图12 多帧实例+激光雷达点云 (俯视+路径) 这一完整流程不仅验证了合成数据在工程流程中的落地能力,也为后续基于大规模仿真生成标准训练集打下了结构基础。 四、aiSim:感知研发全流程平台 在自动驾驶感知系统的开发过程中,仿真平台已逐渐发展为合成数据生产的重要基础设施。 aiSim 通过集成环境建模、传感器仿真、多模态数据输出与标准格式转换等功能, 支持从场景构建到数据集生成的完整流程 。 1、多样场景与数据格式的灵活支持 aiSim 可 精细还原 环视系统中鱼眼相机的安装布局、图像畸变特性及 BEV 视角拼接逻辑,生成 贴近实车采集的高保真图像 。同时,平台有一套 自成体系的仿真数据组织与输出机制 ,涵盖视觉、激光雷达、毫米波雷达等多类型传感器数据及真值标注。支持通过脚本调度 自动批量生成 不同气候、光照、地形和交通条件下的多样化场景,满足大规模训练与边缘场景验证的需求。 2、从物理建模到标签输出的完整链条 借助图形引擎,aiSim 实现了对真实物理光照、材质、阴影和天气的 动态建模 。平台支持相机、激光雷达、毫米波雷达等传感器的物理与几何特性建模,兼容 OpenCV、ROS 等常见开发标准。在数据输出方面,aiSim 支持多传感器同步控制 ,可自动生成对齐的 2D/3D 检测框、语义标签、Ego 轨迹等数据,覆盖感知算法训练常见需求,减少数据清洗与后处理工作量。 3、工程集成与可扩展性 aiSim 提供 图形界面、工具链与开放 API ,方便用户将其集成至企业现有的数据平台和模型训练流程中。平台内的场景配置与资源系统具备良好的 可扩展性 ,支持用户自定义传感器布设、交通要素和场景资产,用于支持环视系统、感知模型、融合算法等不同研发阶段的需求。 无论是 环视系统的泊车能力 与 虚拟标定 ,还是面向 NOA 和多模态融合 的训练任务, 仿真生成的数据 都在感知系统的实际落地中提供了可衡量、可扩展的价值。让数据获取从“拍”到“造”,从“靠人”到“自动”,为智能驾驶研发提速、降本、增稳。

标签: 仿真

标签: 仿真