高速先生成员--黄刚

引言不多说,直接进入正题!大家如果对PCB板厂的加工能力有了解的话,都很清楚,目前主流的板厂会将传输线阻抗控制公差在±10%这个范围,然后有几家一线板厂有能力做到±8%,感觉目前国内的板厂应该还没有正式承诺能做到±5%的吧。至于原因嘛,高速先生之前的文章:掌握了这个分析方法,实现传输线阻抗5%的加工公差不是梦!其实已经有提过,上面提到的PCB传输线结构的各种误差都会积累起来,从而导致整体的阻抗误差增大。目前看起来5%的阻抗控制的确还属于可遇而不可求的情况!

然而国外的一个大客户最近向我们提出了一个比阻抗±5%还能苛刻的要求,他们希望在他们的测试夹具中做到高速线的阻抗±5%,还有一个可能95%的夹具项目都没有的要求,就是高速线的损耗也要保证±5%的误差!

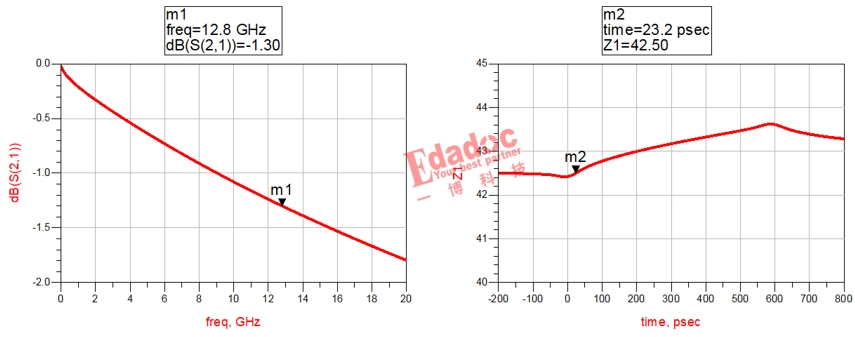

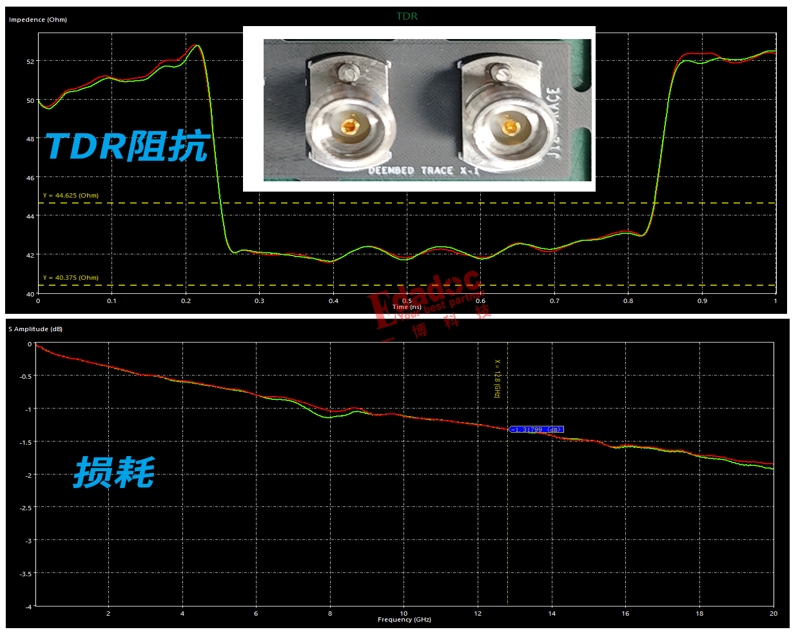

是的,国外的客户一向都是要求比较严格,它提出的要求,可能Chris之前真的没有听过!阻抗要求满足5%的要求,损耗要求在12.8GHz达到1.3dB±0.05dB。一个字,难!一个英文单词,impossible!

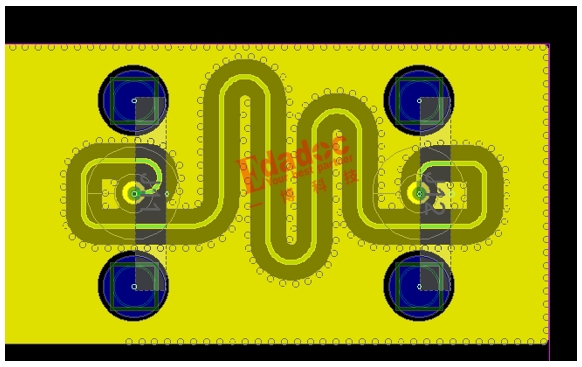

客户要保证的阻抗和损耗是下面这条夹具的链路,单端42.5欧姆的链路。

毕竟这个客户也合作很多很多年,既然他们有这个需求,又一定程度上做好了不行的心理准备,那就作为一个预研的项目了,说干就干!

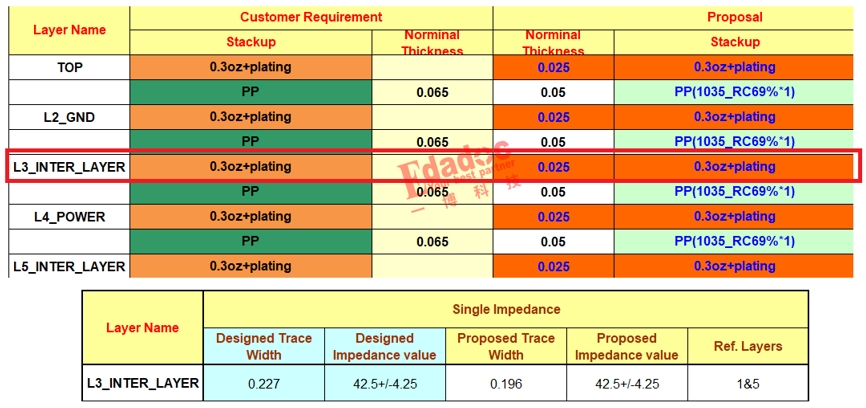

首先从叠层开始就抓得很严格,内层走线,线宽尽量宽点,用上多次验证后有把握的板材和性能好的PP,大概定下来这样的叠层。走线在L3层,隔层参考TOP和L5层,使线宽增大,控制线宽导致的阻抗和损耗误差。

叠层定下来之后,输入叠层和线宽板材参数信息,先仿真得到理想加工情况下的阻抗和损耗。在确定线长为某一数值的情况下,在仿真中让链路满足了损耗和阻抗的指标。

但是上面也仅限于在仿真中满足,其实意义不大,只能认为是在中值情况下能满足。我们需要分别进行DOE仿真,从理论上探讨加工误差影响阻抗和损耗的因素。

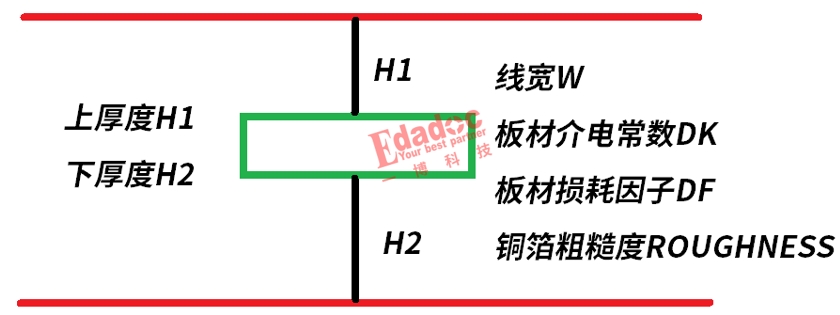

首先无论是阻抗还是损耗,我们在PCB结构和板材的参数定义以下6个参数。

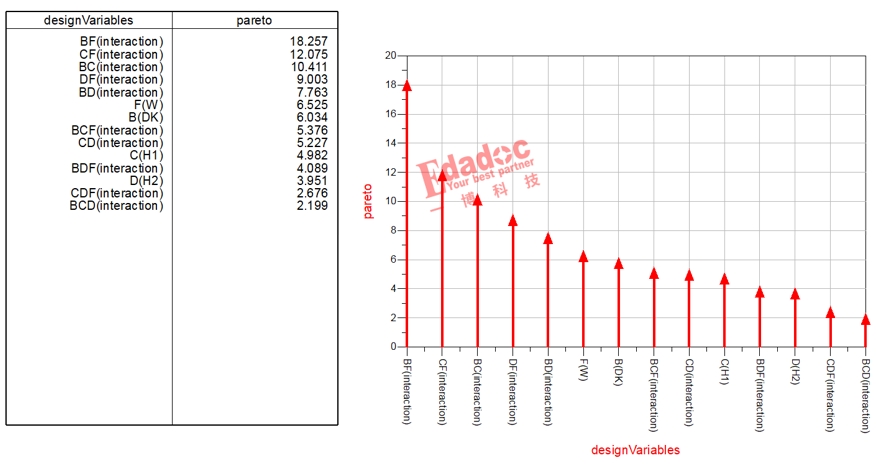

从阻抗的DOE分析中,我们可以看到不同参数的影响比例如下:和Chris的认知也比较吻合,除了DF和粗糙度基本没影响外,其他4个因素都有一定的影响,而且基本还是互相交互的影响。

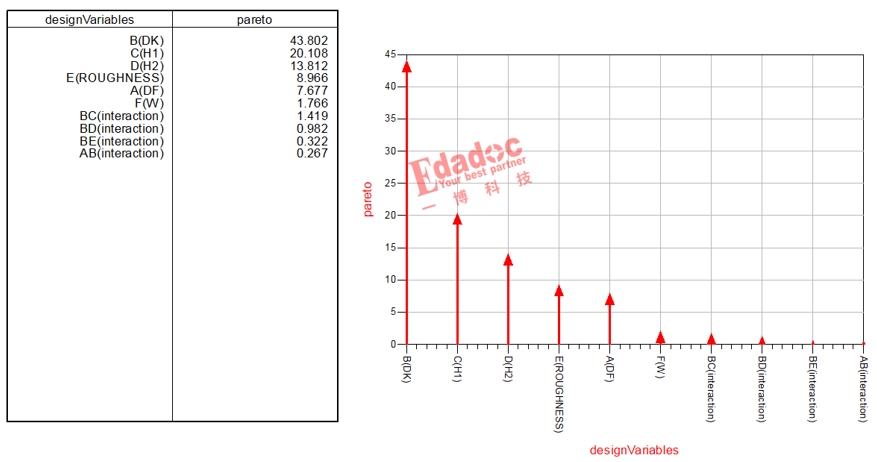

而对损耗的DOE仿真,我们能看到更多新的知识点。除了我们认知中的板材DF和铜箔粗糙度,包括线宽W会影响损耗外,让人没想到的是,阻抗的变化居然也对损耗有非常大的影响,所以你们能看到板材的介电常数DK居然排在影响榜的第一位,上下厚度也是名列前茅。

Chris综合了两个指标的影响偏差因素后,就开始配合我们的板厂去做一些加工的侧重点,尽量去减小加工的误差,当然这个项目加工的可控度也远比嘴上说的要难,最后经过了一段不短时间的努力,终于达到了目标。加工回来后,我们抽测了2块板子,阻抗和损耗都完美的达到了客户的要求,而且一致性非常好,说明这批次的加工应该都能满足要求。

当然最后再说一句,通过一些非常规的加工控制方法是有机会同时实现阻抗和损耗的指标,但是非常非常难,需要付出的成本和精力也比较高,因此大家也没必要一定要往这个极端的指标去做,根据自己产品的裕量,量力而行就可以了。实在有像这个世界500强客户一样那么高的指标,找下高速先生吧,或者我们也能帮大家实现哦!

/3

/3