名词解释,请写出下列简写的英文全名或中文意义。

ECO: Engineering Change Order(工程设计更改)

DFM: Design for manufacturability(可制造性设计)

AMBA: Advanced Microcontroller Bus Architecture(先进的微控制总线构架)

DLL: Delay Locked Loop(数字延迟锁相环)

BIST: Built-in Self Test(内建自测)

LDPC: Low Density Parity Check Codes(低密度奇偶校验码)

DCT: Discrete Cosine Transform(离散余弦变换)

STA: Static Timing Analysis(静态时序分析)

CRC: Cyclic Redundancy Check(循环冗余校验码)

2、 请用流程图的方式简述数字ASIC设计流程以及相应的工具。

功能要求 行为设计 行为仿真 综合、优化——网表 时序仿真 布局布线——版图 后仿真 流片

典型ASIC 设计具有下列相当复杂的流程:

u 结构及电气规定。

u RTL级代码设计和仿真测试平台文件准备。

u 为具有存储单元的模块插入BIST。

u 为了验证设计功能,进行完全设计的动态仿真。

u 设计环境设置。包括使用的设计库和其他一些环境变量。使用Design Compiler工具,约束和综合设计,并且加入扫描链(或者JTAG)。

u 使用 自带静态时序分析器,进行模块静态时序分析。

u 使用Formality工具,进行RTL级和综合后门级网表的Formal Verification。

u 版图布局布线之前,使用Prime Time工具进行整个设计的静态时序分析。

u 将时序约束前标注到版图生成工具。

u 时序驱动的单元布局,时钟树插入和全局布线。

u 将时钟树插入到DC的原始设计中。

u 使用Formality,对综合后网表和插入时钟树网表Formal Verification。

u 从全局布线后的版图中提取出估算的时间延时信息。

u 将估算的时间延时信息反标注到 Design Compiler或者Prime Time。

u 在Prime Time 中静态时序分析。

u 在Design Compiler 中进行设计优化。

u 设计的详细布线。

u 从详细布线设计中提取出实际时间延时信息。

u 将提取出的实际时间延时信息反标注到Design Compiler或者Prime Time中。

u 在Prime Time进行版图后的静态时序分析。

u 在Design Compiler中进行设计优化(如需要)。

u 进行版图后带时间信息的门级仿真。

u LVS和DRC验证,然后流片。

3、a.数字电路的静态功耗和动态功耗有哪几部分构成?与哪些因素有什么关系。

b.阈值电压Vt对静态功耗有什么影响?对电路速度有什么影响?

请阐述动态时序和静态时序分析的区别和各自的作用。

动态功耗:主要是指晶体管开关状态变换产生的开关功耗,还包括输出电压转换的过程中NMOS和PMOS同时导通造成的短路电流功耗。与电源电压的平方,以及总负载电容,时钟频率,动态转换因子的大小成正比。

静态功耗:即晶体管状态稳定不变时的功耗,包括:亚阈漏电流功耗,多晶硅栅漏电流功耗,PN结反偏漏电流功耗。与电源电压成成正比,与阈值电压成指数关系。

提高阈值电压Vt可以有效地降低静态功耗。但提高阈值电压,电路的速度会降低。

动态时序分析的时序确认通过仿真实现,分析的结果完全依赖于验证工程师所提供的激励。不同激励分析的路径不同,也许有些路径(比如关键路径)不能覆盖到,当设计规模很大时,动态分析所需要的时间、占用的资源也越来越大。

静态时序分析根据一定的模型从网表中创建无向图,计算路径延迟的总和,如果所有的路径都满足时序约束和规范,那么认为电路设计满足时序约束规范。静态时序分析的方法不依赖于激励,且可以穷尽所有路径,运行速度很快,占用内存很少。它完全克服了动态时序验证的缺陷,适合大规模的电路设计验证。对于同步设计电路,可以借助于静态时序分析工具完成时序验证的任务。

4、a.解释setup time 和 hold time 的定义。

b.如果一个电路中的某个time path有setup time violation。请问升高或降低这个电路的频率对这个violation有什么影响?升高或降低这个电路的电压会有什么影响?

c. 如果一个电路中的某个time path 有hold time violation。请问升高或降低这个电路的频率对这个violation有什么影响?升高或降低这个电路的电压会有什么影响?

常考题!!!!

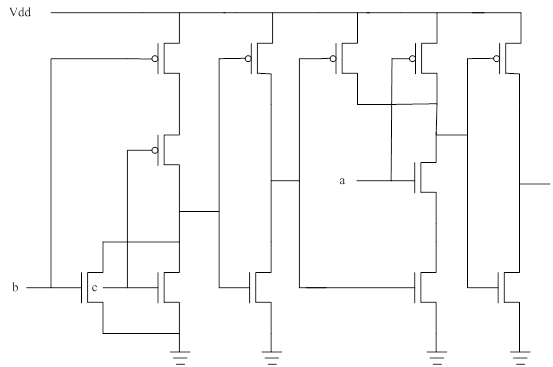

5、画出![]() 的CMOS 电路图。

的CMOS 电路图。

6、画出一下RTL code 对应的门级电路图,请使用最少的门。并且只能使用与门and,或门or 和非门not。a 是2-bit输入,b是1-bit输入,c是1-bit输出。

case(a[1:0])

2'h0:d = b;

2'h1:d = c;

2'h2:d = 1'b1;

2'h3:d = 1'b0;

Endcase

这题大家自己琢磨了啊!!!!

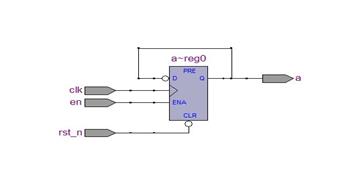

7、画出一下三段RTL code对应的电路图。

(a) always @(posedge clk or negedge rst_n)

if(!rst_n)

a <= 1'b0;

else if(en)

a <= ~a;

|

|

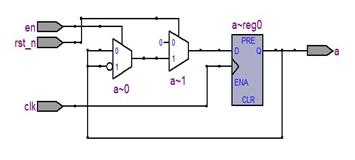

(b) always @(posedge clk)

if(!rst_n)

a <= 1'b0;

else if(en)

a <= ~a;

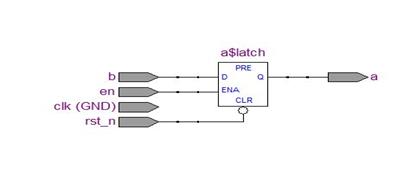

(c) always @(rst_n or en or b)

if(!rst_n)

a <= 1'b0;

else if(en)

a <= b;

/5

/5

用户1840696 2015-8-23 14:51

用户1742568 2014-3-29 14:16

用户1327305 2013-11-19 09:08