8、用HDL设计一个模块。完成有符号数除法,被除数为16-bit整数,除数为8-bit整数,输出8-bit商和8-bit余数,所有输入输出都是有符号数。

module div_16(clk,rst_n,a,b,c,d,div_out,p,div_c);

input clk;

input rst_n;

input [15:0] a;

input [7:0] b;

output [7:0] c;

output [7:0] d;

output [7:0] div_out;

output p;

output [6:0] div_c;

wire [15:0] div_a;

wire [7:0] div_b;

wire p;

reg [7:0] div_c;

reg [7:0] div_d;

wire [7:0] div_out;

assign div_a = (a[15] == 0) ? a : {a[15],~a[14:0]+1'b1};

assign div_b = (b[7] == 0) ? b : {b[7],~b[6:0]+1'b1};

assign p = a[15] ^ b[7];

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

div_c <= 8'b0;

div_d <= 8'b0;

// div_d <= 8'b0;

end

else begin

div_c <= div_a[14:0] / {div_b[6:0]};

div_d <= div_a[14:0] % div_b[6:0];

end

end

//assign div_c = div_a[14:0] / div_b[6:0];

//assign div_d = div_a[14:0] % div_b[6:0];

assign div_out = {p,div_c[6:0]};

assign c = (div_out[7] == 0) ? div_out : {div_out[7],~div_out[6:0]+1'b1};

assign d = div_d;

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

div_c <= 8'b0;

div_d <= 8'b0;

// div_d <= 8'b0;

end

else begin

div_c <= div_a[14:0] / {div_b[6:0]};

div_d <= div_a[14:0] % div_b[6:0];

end

end

//assign div_c = div_a[14:0] / div_b[6:0];

//assign div_d = div_a[14:0] % div_b[6:0];

assign div_out = {p,div_c[6:0]};

assign c = (div_out[7] == 0) ? div_out : {div_out[7],~div_out[6:0]+1'b1};

assign d = div_d;

endmodule

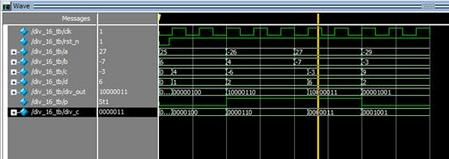

这样写的话基本就对了,还有一种写法是针对使用verilog-2001的,使用signed有符号定义,但modelsim仿真有点问题,我先贴出代码和仿真图先:

module div_8(clk,rst_n,a,b,c,d);

input clk;

input rst_n;

input signed [15:0] a;

input signed [7:0] b;

output signed [7:0] c;

output signed [7:0] d;

assign c = a / b;

assign d = a % b;

endmodule

你们估计看到了,若是使用这种写法的话,得到的模都是负值,后来我查了资料,模值是和第一个数的正负一样,就是和被除数是一样的。除非都是正值,不然还是有问题的。

/5

/5

文章评论(0条评论)

登录后参与讨论