1. 用Verilog HDL语言描述一个32倍分频电路,并画出电路图。

module clk_32(input clk,

input rst_n,

output clk_out

);

reg [3:0] cnt;

always @(posedge clk or negedge rst_n)

if(!rst_n) cnt <= 4'b0;

else if(cnt == 15) cnt <= 1’b0;

else cnt <= cnt + 1'b1;

always @(posedge clk or negedge rst_n)

if(!rst_n) clk_out <= 1'b0;

else if(cnt == 15) clk_out <= ~clk_out;

else clk_out <= clk_out;

endmodule

这一题是常见题,但也有难度,就是要画出电路图,我没画了。

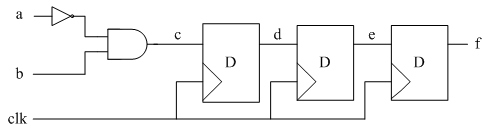

2. 根据verilog语句画出电路图。

1) always @(posedge clk) begin

c <= !a & b;

d <= c;

f <= d;

end

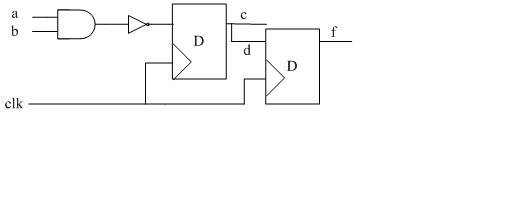

2) always @(posedge clk) begin

c = !(a & b);

d = c;

f <= d;

end

阻塞和非阻塞的区别,刚学verilog的时候,我们都知道,但过了这么久了,我还是想了很久才做出来。

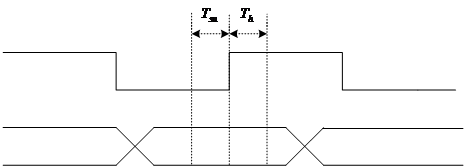

3、考察对建立时间和保持时间的理解,并分别画出波形图说明,如果建立时间不够,为什么,该怎么解决;如果保持时间不够,为什么,该怎么解决。

建立时间:是指时钟上升沿到来之前,数据必须保持稳定的时间。

保持时间:是指时钟上升沿到来之后,数据必须保持稳定的时间。

![]() 如果建立时间不过,即建立时间余量不够,可以增大时间周期,或者是减少寄存器间组合逻辑

如果建立时间不过,即建立时间余量不够,可以增大时间周期,或者是减少寄存器间组合逻辑![]() 。

。

![]() 如果保持时间不够,可以增大寄存器间组合逻辑

如果保持时间不够,可以增大寄存器间组合逻辑![]() 。

。

建立时间和保持时间,几乎我参加的笔试题中都有这中类型的题目,可见,公司对时许约束的要求还是很高的。

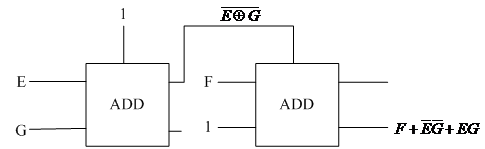

4、请用两个全加器搭建如下布尔逻辑电路:

![]()

![]()

![]()

这道题,真是很郁闷,当时做的时候,没有化简到最简式,回校的时候再琢磨做出来的,最原始的数字题目啊,真是相当丢人。

5、分析嵌入式cpu的功耗,怎么降低功耗,还有分析单核和多核cup的区别。

静态功耗:待机功耗+静态功率。待机功耗:CMOS的漏电流带来的功耗;静态功率:随着集成电路工艺的进步,问题越来越突出。

动态功耗= ![]() 。

。

这个我就完全不知道了,嵌入式功耗,感觉自己知识面很窄。

附加题:6、分析YUV420,YUV422,VGA565,VGA888的区别。

4:2:2 表示 2:1 的水平取样,没有垂直下采样。

4:2:0 表示 2:1 的水平取样,2:1 的垂直下采样。

7、常见的显示器类型和显示接口类型。

显示器类型:CRT,LCD,LED,OLED; 显示接口类型:VGA,DVI,HDMI。

附加题都是视频处理相关的,我有点理解,但还是写不全。

总结:每次到科大去参加宣讲会,其实,我是抱着被鄙视的心态去的。我的数字IC这个岗位,要求还是挺高的,自我感觉,高不成低不就。答题不够完美,我还需努力。我近一个月,参加了不少的招聘会了,但每次都没有认真的总结,这是第一次,当然也不是最后一次,以后每有心得,我要用语言记录下来,记录这段我找工作的历程,为自己加油打气。

用户1721541 2015-8-29 11:27

用户1656142 2013-10-28 22:51

用户377235 2013-10-22 23:42

用户1619789 2013-10-22 20:51

用户425250 2013-10-22 12:40