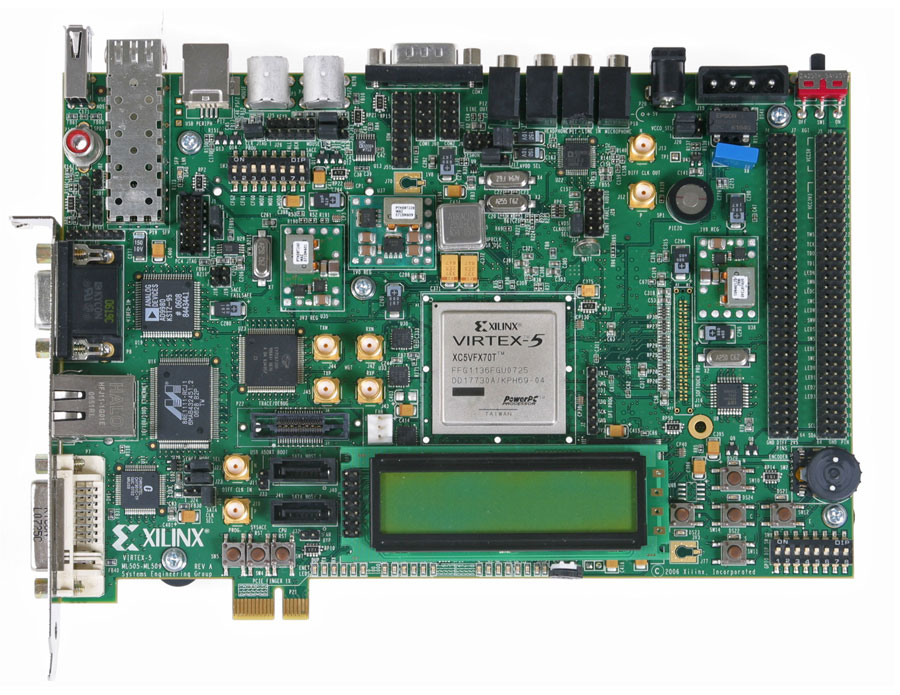

搬到老校区已有一周了,这学期我的主要任务是做毕业设计,题目是用FPGA实现宽带信号的可靠传输,其实题目上学期已经拿到,但之前一直在做38所DSP函数库的项目,因此也就没有时间准备这个课题,不过觉得挺有意思的,可能是做软件做的时间比较长,想换换口味了。寒假回家查了查FPGA高速通信方面的一些资料,找到的信息不是很多,但基本上知道我要做什么了,对课题有了一个了解。开学后导师给我们了一块实验板,是Xilinx V5系列的。之前没有接触过

FPGA,拿到这个实验板,觉得很兴奋,觉得这个板子太酷了,在网上一查,1195美元,折合人民币8000多呢,我的天呢,比我的笔记本电脑还贵呢,我下定决心,一定要把这玩意搞懂,搞精!

一周过去了,每天都在实验室泡着,刚开始都不知怎么从哪入手,更别提拿这个板子实现什么功能了。我花了几天时间,将VHDL语言复习了一遍,其实以前学过这个语言,现在再熟悉熟悉。再花了一些时间,将ISE软件学习了一遍,按照书上的方法操作了几遍,知道大概的开发过程,但这个软件功能十分强大,我只是略知皮毛而已,不过对于初学者已经够用了,其他高深的东西以后遇到了再学不迟。语言和开发环境都熟悉了之后,我就想做点具体的东西了,首先想到的就是控制一下板子上的LED,这个是比较基础的实验,我大概构思了一下,将端口定好,使其输出“00000001”,并且使其不断循环移位,这样就可以做一个流水灯了,但问题也就随之而来,板子上的时钟是100MHz的,如此高的频率怎么控制呢,我想到了分频,用一个计数器计数,这样可以实现延时,我写的代码如下

process(clk)

begin

if(rising_edge(clk)) then

count<=count+'1';

end if;

if(count(30)='1') then

led<=num;

count<=(others=>'0');

num<=num(6 downto 0) &num(7); --循环移位

end if;

end process;

我将其进行了功能仿真,得到的波形完全正确,觉得万无一失了,就将其下到板子上,结果只见灯闪了几下就不动了,当时很是郁闷,查了又查,程序和仿真波形都没什么问题啊,接下来我想到了管脚约束,查了一下,管脚果然约束错了,将其修改后,我得意地又下载了一遍,还是有问题,这时已经晚上10:30了,时候不早了,我就不舍地离开了。

第二天早上来后,我迫不及待地又查了查程序,将其修改如下

process(clk)

begin

if(rising_edge(clk)) then

count<=count+'1';

if(count(30)='1') then

led<=num;

count<=(others=>'0');

num<=num(6 downto 0) &num(7); --循环移位

end if;

end if;

end process;

经过漫长的编译生成了bit文件,下载到板子后,发现8个LED流动闪烁了起来,当时真的是非常激动,终于成功了,我的第一个上板程序调试成功!哈哈……高兴不能太早,还没找到问题的所在,在这里我向大家求助,到底是什么问题导致第一个程序不能成功呢?

这周结束了,下周我将继续努力!争取可以控制板子上的LCD液晶显示。

/3

/3

用户1528479 2010-4-18 20:17