我遇到了一些电平转换的问题,主要是3.3V的ARM和5V或者3.3V的CPLD还有5V也可以是3.3V的AD9822,最后是5V的CCD之间的关系。

想来想去,最后最好的结果还是使用3.3V的ARM,CPLD还有给AD的逻辑,还有所有的缓冲芯片和SRAM供上3.3V的电平,这样做的最大好处,就是只需要在CCD和做一个电平转换就可以了。

对于这个整理了一些资料:

A器件=>B器件

对于逻辑电平来说,最主要的有以下四个参数:

B器件的输入参数

输入高电平(VIH):逻辑将输入电压识别成高电平时所允许的最小输入高电平,当Vinput>VIH时,则逻辑为高电平。 注意当输入电平为高时候,往往存在输入级有一定的泄漏电流,这个数值非常小在uA范围内,Ileak。

输入低电平(VIL):逻辑将输入电压识别成低电平时所允许的最大输入低电平,当Vinput<VIL时,则认为输入电平为低电平。 注意当输入电平为低时候,往往存在输入级有一定流出的泄漏电流,这个数值非常小在uA范围内,Ileak。

泄流电流是钳位二极管和输入MOS管的综合作用。

A器件的输出参数

输出高电平(VOH):在一定的输出电流(流出)下,逻辑门的输出为高电平时的输出电平的最小值。由于可等效成内部的Rdson,实际上这个数值并没有大的意义,因为只有我们考虑了Rdson才能真实的估计实际的输出高电平的数值。

输出低电平(VOL):在一定的输出电流(注入)下,逻辑门的输出为低电平时的输出电平的最大值。同上面一个参数是同样一个概念。

电平兼容的要求

VOH > VIH:在VIH需求的电流下的VOH。

VOL < VIL:如果不存在上拉的条件的话,一般VOL的压降问题不大,这是一个比较容易满足的条件。

当然可能设定一定的电压阈值,作为噪声容限。

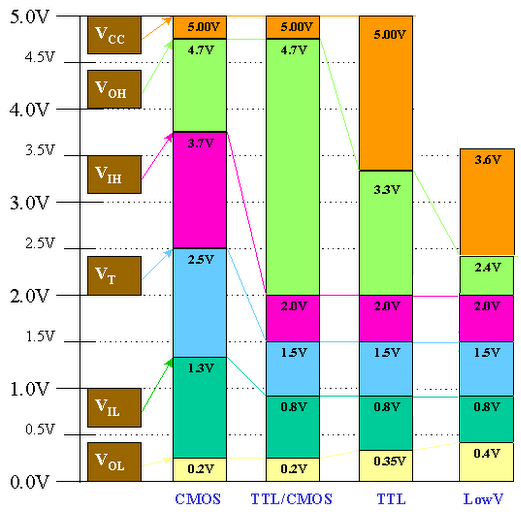

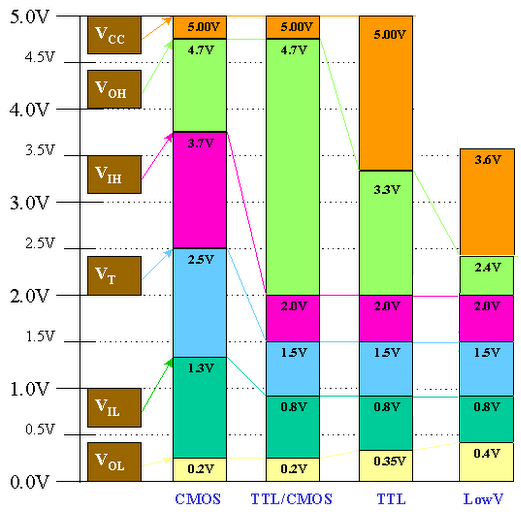

然后我们选取四类逻辑电平:TTL、CMOS、LVTTL、LVCMOS

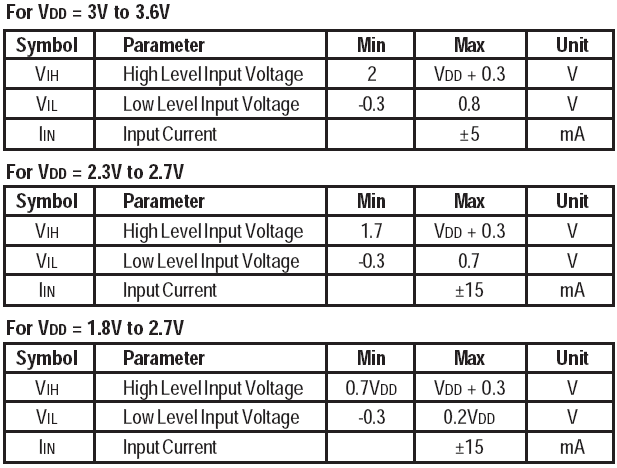

输入参数

CMOS:输入高电平UIH min =(0.65~0.7)×5V,输入低电平UIL max =(0.3~0.35)×5V

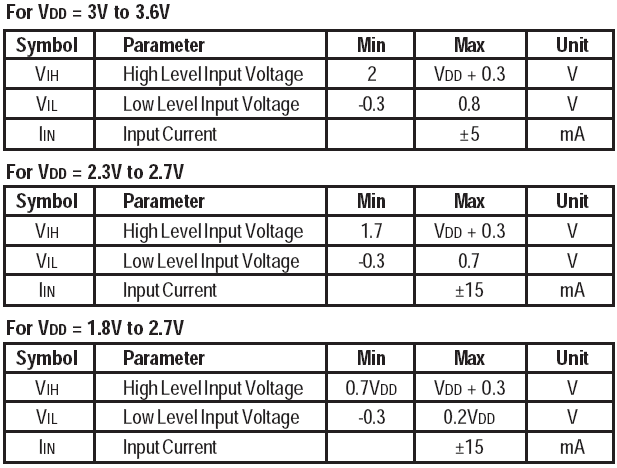

LVCMOS:

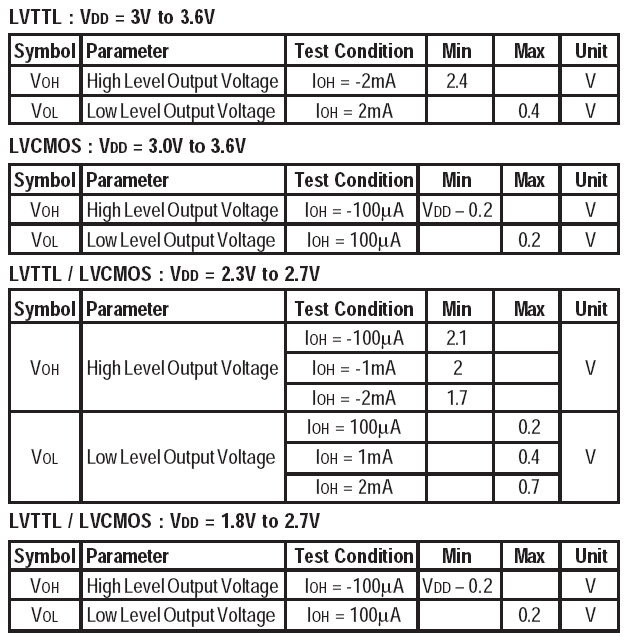

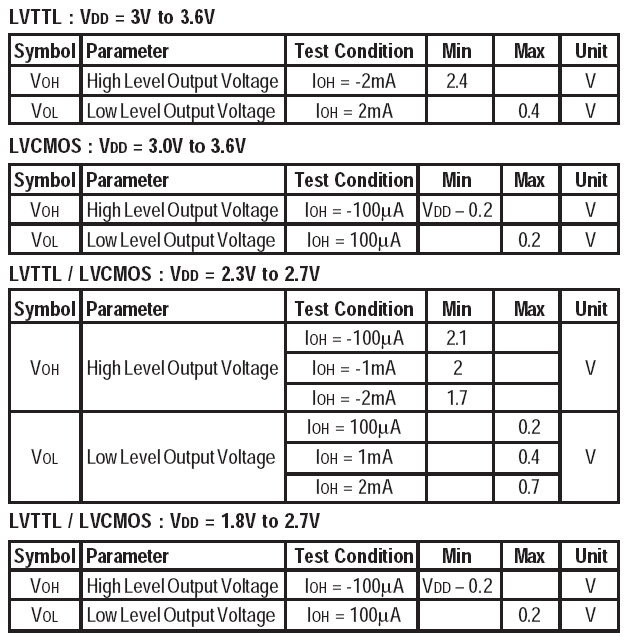

输出参数

一般而言:

CMOS:输出高电平UOH main = VDD-0.2V,输出低电平UOL max = 0.2V.

LVCMOS:

按照正常的情况

LVCMOS输出=>CMOS输入,电平可能太低,导致高电平无法识别。

CMOS输出=>LVCMOS输入,电平可能太高,导致IO口钳位。

目前网上有很多解决电平的方案,仔细分析一下,并对比优缺点和使用范围。

Device Families:

TTL (74xx) True TTL

74L Low power

74S Schottky

74H High speed

74LS Low power - Schottky

74AS Advanced - Schottky

74ALS Advanced - Low power - Schottky

74F(AST) Fast - (Advanced - Schottky)

74C CMOS...................check Vcc levels

74HC (U) High speed - CMOS (Unbuffered output)

74HCT High speed - CMOS - TTL inputs

74AHC Advanced - High speed - CMOS

74AHCT Advanced - High speed - CMOS - TTL inputs

74FCT (-A) Fast - CMOS - TTL inputs (speed variations)

74FCT (-T, -AT) Fast - CMOS - TTL inputs (speed variations)

74AC Advanced - CMOS

74ACT Advanced - CMOS - TTL inputs

74FACT AC, ACT (Q) series

74ACQ Advanced - CMOS - Quiet outputs

74ACTQ Advanced - CMOS - TTL inputs - Quiet outputs

Bus Driver Families

74ABT Advanced - BiCMOS - Technology

74ABTE ABT - Enhanced Transceiver Logic

74ABTH Advanced - BiCMOS - Technology - bus Hold

74BCT BiCMOS - TTL inputs

74BTL Backplane - Transceiver - Logic

74GTL Gunning - Transceiver - Logic

74GTLP GTL Plus

Low Voltage Families

74ALB Advanced - Low Voltage - BiCMOS

74LV (U) Low - Voltage (Unbuffered output)

74LVC (R) LV - CMOS (damping Resistor)(Unbuffered output)

74LVCH Low - Voltage - CMOS - bus Hold

74ALVC Advanced - Low - Voltage - CMOS

74LVT (R) (U) LV - TTL (damping Resistor(Unbuffered output)

74LVTZ Low - Voltage - TTL - High Impedance power-up

74ALVC (R) ALV - CMOS (bus Hold) (damping Resistor)

74ALVCH Advanced - Low - Voltage - CMOS - bus Hold

74LCX LV - CMOS (operates with 3v & 5v supplies)

74VCX LV - CMOS (operates with 1.8v & 3.6v supplies

4000 True CMOS (non-TTL levels)

ECL Device Families:

MEC I 8nS*

MEC II 2nS*

MEC III (16XX) 1nS* .......* = Rise & Fall Times

101xx 100 series 10K ECL, 3.5nS*

102xx 200 series 10K ECL, 2.5nS*

108xx 800 series 10K ECL, voltage compensated, 3.5nS*

10Hxxx 10K - High speed, voltage compensated, 1.8nS*

10Exxx 10K - ECLinPS, voltage compensated, 800pS*

100xxx 100K, temperature compensated

100Hxxx 100K - High speed, temperature compensated

100Exxx 100K - ECLinPS, temp, voltage comp., 800pS*

飞言走笔 2011-3-21 08:26

ilove314_323192455 2011-3-18 10:59

ilove314_323192455 2011-3-18 10:58

用户313191 2011-3-18 09:17

用户235812 2011-3-18 09:08

朱玉龙 2011-3-18 08:38

用户305449 2011-3-18 08:30

用户1584993 2011-3-17 16:52

朱玉龙 2011-3-17 16:28

用户1584993 2011-3-17 15:52