原创

verilog学习笔记【test bench】

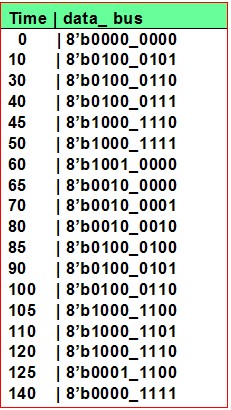

1、在test bench中使用fork...join并行块。它可以声明绝对时间,可以并行的执行复杂的过程结构,如循环或任务。

module inline_ tb;

reg [7: 0] data_ bus;

// instance of DUT

initial fork

data_bus = 8'b00;

#10 data_bus = 8'h45;

#20 repeat (10) #10 data_bus = data_bus + 1;

#25 repeat (5) #20 data_bus = data_bus << 1;

#140 data_bus = 8'h0f;

join

endmodule

2、时钟的产生

initial begin

ck = 0;

#( period)

forever

#( period/2) ck = !ck; //~ck

end

always #10 ck = !ck;//~ck

3、initial块适合产生不规则的激励;循环或者always块适合产生规则的激励。

/7

/7

文章评论(0条评论)

登录后参与讨论