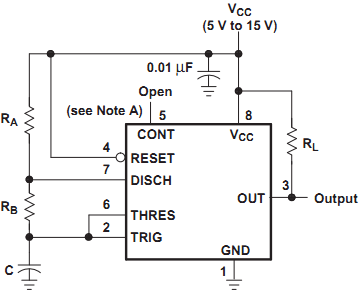

工作原理分析:

电容C可由Ra Rb充电,并由Rb放电占空比乃由Ra和Rb进行控制,电容C的充放电乃是在VCC/3和2VCC/3之间重复进行,过程分析:

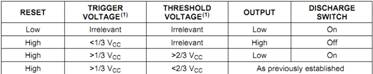

1. 初始UC在略低于VCC/3,此时输出高电平,放电引脚关闭,VCC对C充电时间常数0.693(RA+RB)C;

2. 冲电到略高于VCC/3,参考真值表输出保持之前高电平,放电引脚关闭,VCC对C充电时间常数1/(RA+RB)C;

3. 充电到略高于2VCC/3,输出低电平,放电开关打开,C放电时间常数1/RB*C;

4. 放电到略低于2VCC/3,进入保持态,C放电时间常数0.693RB*C;

5. 放电到略低于VCC/3进入1循环

整个过程从而呈现

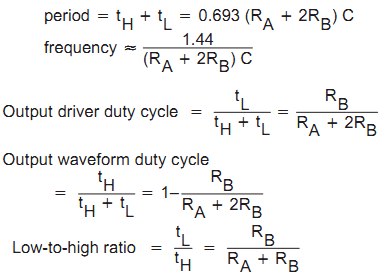

高电平时间:经RA,RB充电VCC/3到2VCC/3的时间;

低电平时间:经RB从2VCC/3放电到VCC/3的时间;.

计算公式:

用户1707737 2012-10-12 20:09

谢谢,正在做这个题目,做完了,还会把跟详细的贴出来

用户403664 2012-9-28 11:47

用户377235 2012-7-8 12:11

用户377235 2012-7-7 21:13

用户862116 2012-7-7 12:09

用户278669 2012-7-7 12:04