序列检测器

实验目的:用状态机设计一个序列检测器,实现对序列10010的检测。

状态转换图如下:

图1 序列检测器的状态转换图

对于以上状态图作出如下说明:

(1)各箭头上方的数字表示状态跳转条件及相应的输出结果。如:S0—>S1上的1/0表示当输入的数据为1时,由状态S0跳转到状态S1,并且输出为0,表示还未检测到(或未检测完)数据流10010。同理,当完整地检测到10010时就输出1。

(2)从S0~S5共有六种状态,在设计程序的时候,通常是采用3bit数据类型表示即可,但是,为了适应高速数字电路的应用需求,扩大数据信号的时间窗(时间窗由建立时间和保持时间构成),避免出现不稳定的中间态,故此六种状态采用6bit的数据类型表示。

(3)下面描述一下状态跳转的过程:

S0为起始状态(或默认状态),当第一个bit到来的时候,判断其是否为1,若为1则跳转到S1状态,并输出0作为标志信号,表示序列检测尚未完成;若为0则保持当前状态不变,同时输出标志信号0。

若当前状态为S1,当前输入的bit为0,则状态机跳转到S2状态,并输出标志信号0;若当前输入的bit为1,则保持当前状态不变。

若当前状态为S2,当前输入的bit为0,则状态机跳转到S3状态,并输出标志信号0;若当前输入的bit为1,则状态机跳转到S1状态,并输出标志信号0。

若当前状态为S3,当前输入的bit为1,则状态机跳转到S4状态,并输出标志信号0;若当前输入的bit为0,则状态机跳转到S0状态,并输出标志信号0。

若当前状态为S4,当前输入的bit为0,则状态机跳转到S5状态,并输出标志信号1,检测到一个完整的“10010”序列;若当前输入的bit为1,则状态机跳转到S1状态,并输出标志信号0。

若当前状态为S5,当前输入的bit为0,则状态机跳转到S3状态,并输出标志信号0;若当前输入的bit为1,则状态机跳转到S1状态,并输出标志信号0。

除上述跳转过程外,各状态均需加上一条复位跳转路径,即:当复位信号rst_n当来的时候,任何状态都跳转到S0状态,输出0作为标志信号。

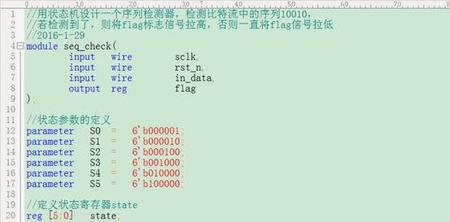

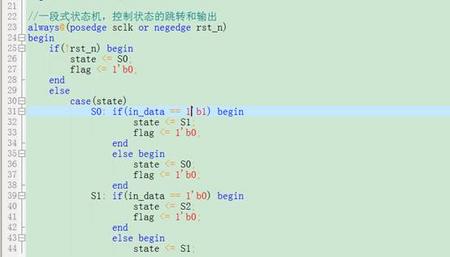

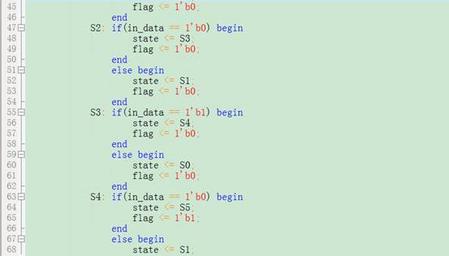

按照上面的状态跳转图写状态机,控制状态跳转和信号输出,程序代码如下截图所示:

接下来是写testbench,代码如下:

以上testbench的目的:

(1)产生频率为50MHz的时钟信号和复位信号;

(2)产生测试需要的比特流序列,该序列为11100011010010100101100100100010,将它们送给序列检测器予以检测。

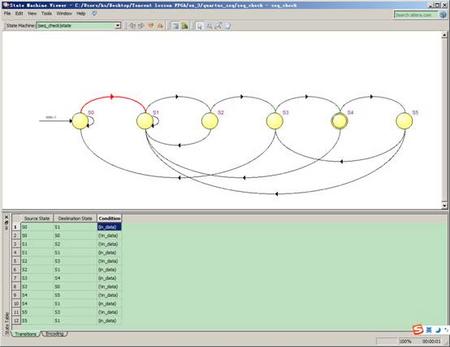

Quartus综合所得的状态转换图如下图所示:

图2 Quartus综合所得的状态转换图

对比图2和图1可知,综合后所得的状态转换图与设计要求中的状态转换图一致,转换条件相同。下面,可以直接看仿真结果,仿真结果如图3所示:

图3 仿真结果截图

由图3可知,in_data是我们产生的比特流,它们是11100011010010100101100100100010,与期望的值是一致的。同时,在对比特流进行序列检测的过程中,flag信号共出现了4次高电平,分别是在i为18与17之间、13与12之间、7与6之间以及4与3之间,这与序列10010在比特流中的位置是一致的(左起是第31位,右起是第0位)。故由此可知,序列检测器的检测功能正常。 /2

/2

文章评论(0条评论)

登录后参与讨论