两段式状态机

实验目的:用两段式状态机描述法设计如图1所示的状态图转换图。

图1 状态转换图

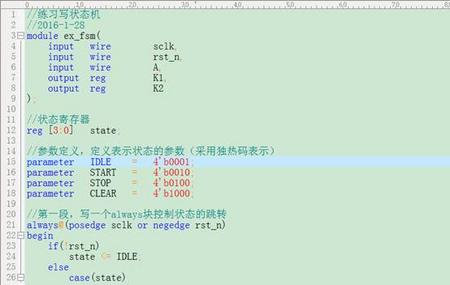

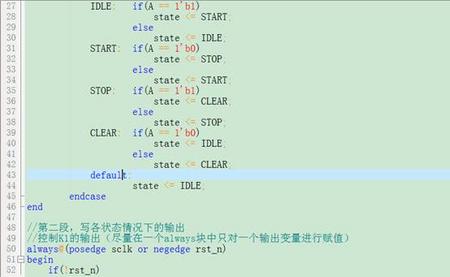

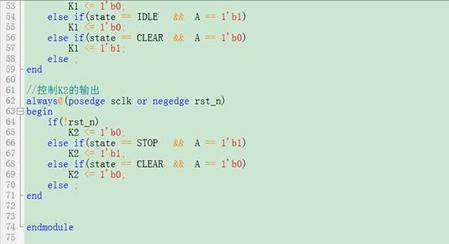

由图1可知,状态的跳转和输出信号的控制不仅与复位信号Reset有关,还与输入信号A有关,同时,输出有K1、K2两个信号,如果采用一段式状态机描述它则会杂乱无章,甚至会出现漏写语句的情况,故为了描述的状态机条理清晰、缜密,我们决定采用两段式状态机描述该状态转换图,第一段用一个always语句块描述状态的跳转,第二段用一个或多个always语句块描述输出信号与输入信号或当前状态的关系。需注意:(1)always的个数不是状态机的段数;(2)always的个数由输出信号的个数决定,一个always块中尽量只对一个输出变量进行赋值(或控制)。代码截图如下:

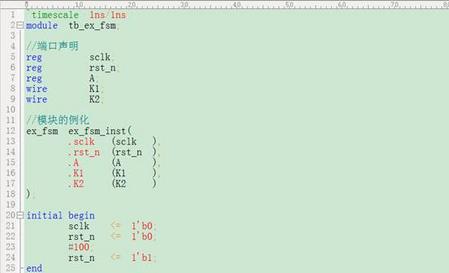

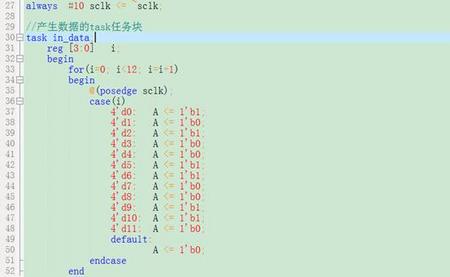

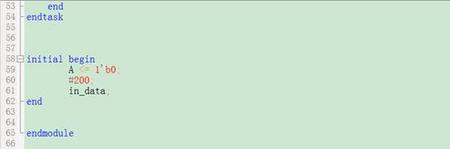

Testbench代码截图如下:

QUARTUS综合得到的状态转换图如图2所示:

图2 QUARTUS综合得到的状态转换图

Modelsim仿真结果如图3所示:

图3 Modelsim仿真结果截图

由图3可知,A从第210 ns开始变为高电平,然后依次产生101001100110的序列(以一个时钟周期为基本单位),在A的作用下,状态机的状态依次经由IDLE、START、CLEAR向STOP跳转,最后由回到IDLE状态。在第290 ns以前,状态每隔一个时钟周期跳转一次;而在第290 ns以后,因为A的电平状态变化减慢,故状态每隔两个时钟周期才跳转一次,K1、K2的高电平保持时间也随之增长。

综上所述,采用两段式状态机描述上述状态转换图调理清晰、思维缜密,验证了状态转换的正确性。

文章评论(0条评论)

登录后参与讨论