深入剖析IO约束续——Output Minmum Delay的计算<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

特权同学在《深入剖析IO约束》一文中提出了对Altera官方基础教程里给出的Output Minmum Delay计算的不同看法。同时也和riple兄进行了一番讨论,结果发现确实是Altera在这里的计算方法有误。而凑巧的是,特权同学在进一步观看Altera官方的《SourceSynchTiming》培训中找到了Output Minmum Delay正确的计算方法。

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

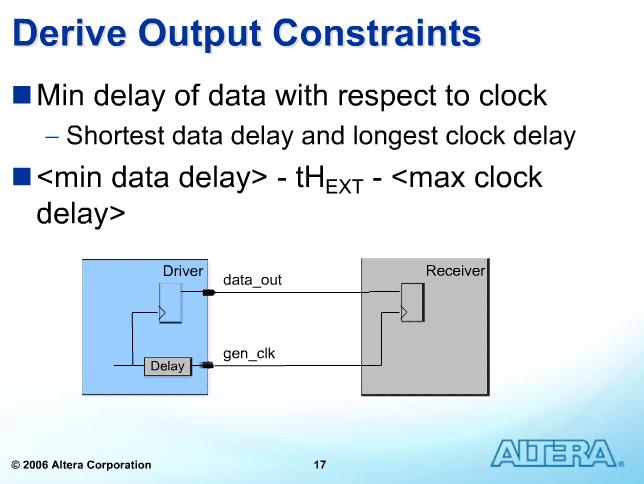

上面的图示中告诉我们:Output Minmum Delay = <min data delay> - 外部器件(右侧)的tH - <max clock delay> 。

<min data delay>是指数据从FPGA器件的输出管脚到达外部器件的输入管脚的PCB延时。<max clock delay>则是指时钟从时钟源传播到外部器件输入端口的PCB延时,对于这个变量,其实对于不同的情况应该要做不同的分析。比如上面的例子里是一个源同步接口(数据和时钟都是由FPGA来产生),那么如果假定FPGA和外部器件连接的数据和时钟信号到达FPGA输出管脚的延时是一样的(实际情况往往不是那么理想,这个以后有机会再讨论),那么这个例子的<max clock delay>就是gen_clk信号从FPGA的输出管脚到外部器件时钟输入管脚的延时。而在《深入剖析IO约束》里给出的最后推导出来的公式:Tco>输出最小延时=Th+PCB布线延时-PCB时钟偏斜(这个公式其实还是不太对,或者不能说不对,只是正负号的问题而已,理解了就好办,下面就要说这个),上面的PCB时钟偏斜其实也就是<max clock delay>的一个特例,因为这里假定了FPGA和外部器件使用一个源时钟。反正需要你理解,然后根据不同的接口做不用的分析。

下面来说为什么我们上次得出的Output Minmum Delay = Th - PCB布线延时 - PCB时钟偏斜 = tH - <min data delay> + <max clock delay>不对(这里的PCB时钟偏斜和<max clock delay>的关系需要换算一下的,PCB时钟偏斜是指时钟在PCB布线上到达外部器件的值减去到达FPGA的值,<max clock delay>恰恰相反,所以加一个负号替代即可)。经过对应两个公式,我们发现原来推导的公式和现在的Output Minmum Delay = <min data delay> - tH - <max clock delay>其实是正负颠倒了。那么哪个是正确的呢?

带着这个疑问,我们先再次寻找Output Minmum Delay的定义,单单从字面上我们可以这么理解:数据信号在FPGA内部从时钟launch到达输出管脚这段延时时间的最小值,它需要满足的关系就是数据传输再快也不能侵占下一级寄存器(外部器件)的保持时间Th。理清了这个关系,我们再看对于Clock Hold Slack Time计算中如何使用这个Output Minmum Delay。

Quartus? II TimeQuest Timing Analyzer,Quartus II 8.1;Volume 3;

Data Required Time其实是说数据需要比这个时间晚到达FPGA的输出引脚,所以用数据实际到达输出引脚时间Data Arrival Time减去这个Data Required Time得出的才是保持时间余量。那么Data Required Time和Output Minmum Delay又有怎样的关系呢?Data Required Time里包括了Latch Edge和Clock Network Delay,这个Latch Edge其实和Data Arrival Time里的Latch Edge其实是时钟的同一个沿(可以参看TimeQuest就一定要搞定——时序分析基本公式),而Clock Network Delay即时钟网络延时是一定要加上的。这里的Output Minmum Delay居然是需要减去的参量?这么咋一看特权也很困惑,那么把今天刚给出来的公式套上去看看吧(或者你用上次的带进去也行,反正总有一个是对的)。

Data Required Time = Latch Edge + Clock Network Delay - (<min data delay> - tH - <max clock delay>) = Latch Edge + Clock Network Delay - <min data delay> + tH + <max clock delay> = Latch Edge + (<max clock delay> + Clock Network Delay) + (tH - <min data delay>)

最后我们把等式右边分成三类变量,Latch Edge这个不说了,(<max clock delay> + Clock Network Delay)这个是时钟有关的参数,数据的锁存都是有赖于时钟的到达,那么时钟的延时必须被计算在内的。最后一类(tH - <min data delay>)则是我们上一次提到的FPGA的Tco > 外部器件的tH - <min data delay>,这里既然是算保持时间的Data Required Time,也就是说数据到达这个端口的最快时间(也即Tco的最大值和其他路径延时之和),那么当然应该是要加上这个tH - <min data delay>,所以在这一番推理之后,我们得出结论:Output Minmum Delay = <min data delay> - tH - <max clock delay>是正确的。

/2

/2

用户1000403 2011-6-30 13:21

用户379271 2011-6-27 16:38

用户211454 2011-2-6 15:29