Synchronous模型和clock jitter

晚上和BOSS一起去球场挥汗如雨了,我在努力多花一些时间熟悉新环境和我的新同事们。虽然最近一个多月都没怎么更新博文,不过多少还是积淀了一些值得分享的知识和经验,尤其是近来这一个月和老师傅一起debug了一个据说倒腾半年没解决的case,虽然问题其实非常简单,但是也让我在这个过程之中收获颇丰。

最近花了很多空余的时间好好研读了一下Spartan-3E的各种ug,在ug331.pdf的DCM部分看到了很多很基本知识点的阐述,虽说这些知识概念已经很深的印刻在我的脑海里了,不过对于很多孩子们来说还是非常值得好好“品味”一番的。下面做一点原汁原味的分享吧(建议各位还是好好拜读原文),不过多的掺杂个人的见解,有不解之处各位看官多多留言讨论。

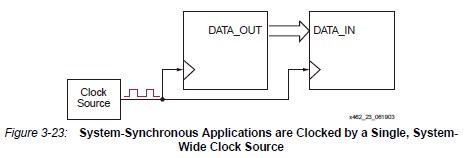

P110讲到clock的skew,其中顺带提到了同步传输中两个基本的模型,即system synchronous和source synchronous。

System Synchronous

In a System Synchronous design, all devices within a data path share a common clock source, as shown in Figure 3-23. This is the traditional and most-common system configuration. The SYSTEM_SYNCHRONOUS option, which is the default value, adds a small amount of clock delay so that there is zero hold time when capturing data. Hold time is essentially the timing difference between the best-case data path and the worst-case clock path. The DCM’s clock skew elimination function advances the clock, essentially dramatically shortening the worst-case clock path. However, if the clock path is advanced so far that the clock appears before the data, then hold time results. The SYSTEM_SYNCHRONOUS setting injects enough additional skew on the clock path to guarantee zero hold times, but at the expense of a slightly longer clock-to-output time.

The extra delay is injected in the SYSTEM_SYNCHRONOUS setting by adding an internal delay on the feedback path. However, there are some situations where the DCM does not add this extra delay, and therefore the DESKEW_ADJUST parameter has no affect. These situations include DCMs that are cascaded, have external feedback, or have an external CLKIN that does not come from a clock input.

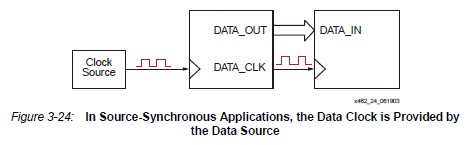

Source Synchronous

SOURCE_SYNCHRONOUS mode is an advanced setting, used primarily in high-speed data communications interfaces. In Source Synchronous applications, both the data and the clock are derived from the same clock source, as shown in Figure 3-24. The transmitting devices sends both data and clock to the receiving device. The receiving device then adjusts the clock timing for best data reception. High-speed Dual-Data Rate (DDR) and LVDS connections are examples of such systems.

The SOURCE_SYNCHRONOUS setting essentially zeros out any phase difference between the incoming clock and the deskewed output clock from the DCM. The FPGA application must then adjust the clock timing using either the Fixed or Dynamic Fine Phase Shift mode.

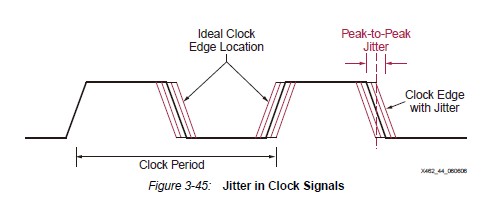

P140提到了clock的jitter,讲解得非常详细。

What is Clock Jitter?

Clock jitter is the variation of a clock edge from its ideal position in time, as illustrated in Figure 3-45. The heavy line shows the ideal position on the clock signal. On each clock edge, there is some amount of variation between the actual clock edge and its ideal location. The difference between the maximum and minimum variations is called peak-topeak jitter. Jitter is only relevant on the active clock edge. For example, in single-data rate (SDR) applications, data is clocked at each rising clock edge and the specified jitter only subtracts from the total clock period. In dual-data rate (DDR) application, data is clocked at the start of each period and halfway into the period. Therefore, jitter affects each half period.

What Causes Clock Jitter?

Clock jitter is unavoidable and exists in all systems. Clock jitter is caused by the various sources of noise or by signal imperfections within the system. In fact, jitter is the manifestation of noise in the time domain. The incoming clock source, for example, has its own jitter characteristics due to random thermal or mechanical vibration noise from the crystal. A large number of simultaneous switching outputs (SSOs) adds substrate noise that slightly changes internal switching thresholds and therefore adds jitter. Similarly, an improperly designed power supply or insufficient decoupling also contributes to jitter.

Other sources of clock jitter include cross talk from adjacent signals, poor termination, ground bounce, and electromagnetic interference (EMI).

ilove314_323192455 2012-7-29 13:43

用户1531838 2012-7-25 07:37

用户196964 2012-6-20 19:05

ilove314_323192455 2012-6-17 22:11

suphuanben_930628287 2012-6-17 20:53