SF-VGA模块购买地址:http://myfpga.taobao.com/

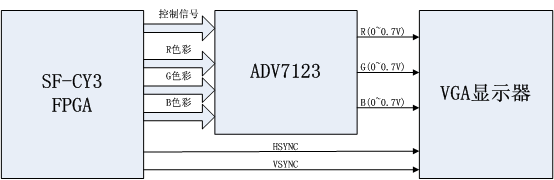

SF-VGA模块板载VGA显示器DA转换驱动芯片AVD7123,FPGA通过OUPLLN连接器驱动ADV7123芯片产生供给VGA显示器的色彩以及同步信号。SF-CY3核心模块与SF-VGA子模块连接的系统框图如图所示。FPGA产生ADV7123的同步信号以及3组供给ADV7123内部3路并行DA的数字信号,经过ADV7123的这3组VGA色彩数字信号最终转换为0~0.7V的模拟电压送给VGA显示器。而FPGA另外会产生用于同步色彩数据的场同步信号VSYNC和行同步信号HSYNC。

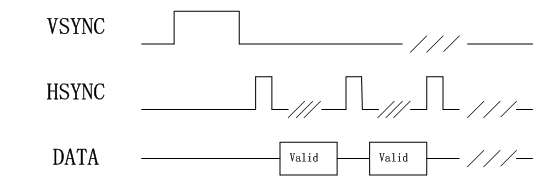

驱动VGA显示的接口,主要有以下3种信号:行同步信号HSYNC,场同步信号VSYNC和数据总线。数据的同步是靠前面两个信号来协助的。至于HSYNC和VSYNC和数据总线之间以什么样的关系进行传输,这都是相对固定的,虽然VGA收发双方没有时钟信号做同步,但我们通常会约定发送方有一个基本的时钟,VSYNC、HSYNC和数据都会按照这个时钟的节拍来确定状态。

VGA的接口时序如图所示,场同步信号VSYNC在每帧(即送一次全屏的图像)开始的时候产生一个固定宽度的高脉冲,行同步信号HSYNC在每行开始的时候产生一个固定宽度的高脉冲,数据在某些固定的行和列交汇处有效。

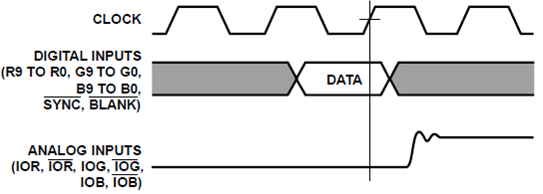

对于ADV7123来说,在它的输入管脚上,理想的时钟和数据波形如图所示。在驱动时钟LCD_CLK信号的上升沿,将对所有的数据和控制信号进行锁存。

![]()

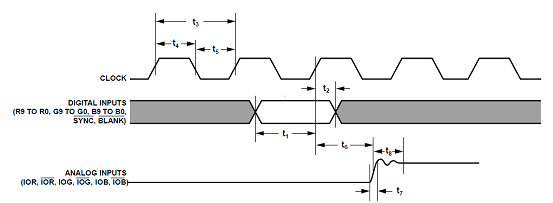

我们还要进一步关心这些数据锁存时相对时钟信号的建立时间和保持时间。再来看下面这个图,这里所示意的t1其实就是数据的建立时间,而t2则是数据的保持时间。

从对应的时序表中,我们找到了t1>0.2ns,t2>1.5ns这样的信息。

![]()

/2

/2

文章评论(0条评论)

登录后参与讨论