文中实例配套SF-CY3开发套件。更多内容请参考《SF-CY3 FPGA套件开发指南》。

接着,我们要来实际应用这些理论,看看实际工程中如何对这些错综复杂的关系进行分析和处理。如图所示,我们这个例程的分频计数实验中使用了一个时钟信号clk,每一次计数都是基于这个时钟的上升沿。

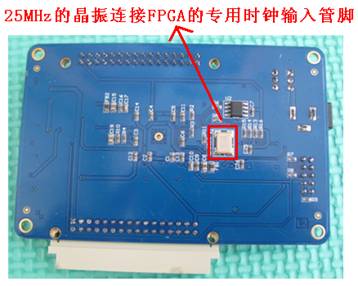

这个时钟哪里来?它的时钟频率如何确定?拍脑袋随便设?非也,咱做事一定要有依有据。如图所示,我们的SF-CY3板载了一颗25MHz的有源晶振,通过管脚分配,我们便将这个时钟引入了设计中。因此,我们这个设计的时钟便要约束为25MHz,即40ns的时钟周期。

好,下面我们就动手为这个实例添加时序约束。如图所示,我们点击工具栏的一个闹钟模样的图标便可打开Quartus II内嵌的时序设计TimeQuest,我们接下来的时钟约束设置便是在该工具中完成的。

TimeQuest的主界面如图所示,首先需要新建一个sdc文件,然后在该文件中输入时钟约束脚本,或者使用GUI进行约束设置更新到sdc文件中。

点击菜单栏NetlistàCreate Timing Netlisk,弹出的菜单中使用默认设置,点击OK便可。接着进行时钟约束,点击菜单栏ConstraintsàCreate Clock。Clock name是我们随便给约束的信号起的名字,没有特别限制;Period为时钟周期,我们的时钟晶振是25MHz的,即40ns;Targets选择实际被约束的时钟管脚,点击改行最后面的按钮可以选择相应的管脚信号;SDC command无须设置,自动根据前面的设置生成,Waveform edges也无须设置,我们采用默认设置,即0ns时钟上升,20ns下降。点击Run完成约束设置。

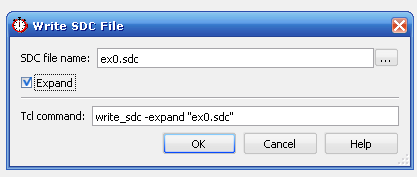

接下来,我们要依次点击主界面右下方task栏里的Update Timing Netlist和Write SDC File选项,弹出的Write SDC File窗口如图所示,我们更改SDC file name为ex0.sdc,接着点击OK。

此时,我们可以在工程目录下找到一个ex0.sdc的文件,并且这个文件里面有一条这样的时钟约束语句:create_clock -name {SYS_CLK} -period 40.000 -waveform { 0.000 20.000 } [get_ports {clk}]。这便是我们前面所添加的约束。

接着回到Quartus II,重新对工程进行编译。接着再进入TimeQuest,点击Report下的Report All Core Timings。

在Report窗口中,出现了Report Timing(Core)一栏,下拉后,我们便可以看到SYS_CLK时钟的Setup和Hold路径的分析。先点击Setup一栏,我们看到右侧齐刷刷的把所有的路径都罗列了一通。这便是SYS_CLK时钟的所有相关Setup路径分析情况,打头第1条是Slack最差的情况,喔……,居然还有36ns多,可谓余量“富得流油”。

再看Hold路径,如图所示,Slack最差的只有0.464ns,正应了前面所说的,Hold和Setup是一对“鱼和熊掌”,或者更形象一点,那叫做“跷跷板的两端”。二者平衡当然是最佳状态,可惜很多时候咱说得不算,大趋势咱改变不了,顶多小范围微调。不过,不用担心,有正余量就OK了,说明设计本身的时序是不存在隐患的。

好,看完宏观局势,我们再来瞄一眼微观情况。如图所示,这是一条setup路径的详细分析。回头可以对照前面给过的公式,把这个路径里面的各个参数对应一代,还真那么回事哦。不过有一点笔者也深感困惑,就是那个uTsu,公式里明明是“-”,而分析中却变成了“+”。公式从理论上讲是肯定不会错,所以为了“套”一下公式我们只能吧正分解为“夫妇”(负+负)了。之说以这么推测,从笔者接触Quartus II开始,大概7到现在的13,这个地方的TimeQuest分析好像一直没有“纠正”过,那么我觉得Altera这么个大厂也不至于老犯这么低级的错误吧,所以,这里面一定“暗藏玄机”。个人猜想,还未官方求证。待我发个邮件有回复了再分享给大家。

Data Arrival Time = Launch Edge + Tc2t + Tco + Tc2r

= 0 + 2.733 + 0.261 + (0.858-0.261)

Data Required Time = Latch Edge + Tc2r – Tsu

= 40 + 2.651 – (-0.021)

Setup time slack = Data Required Time – Data Arrival Time = 42.672 – 3.591 = 39.081ns

再看Hold路径的详细分析,也是对照前面的公式,我们可以一一对应。通过这种实际分析,希望能够加深大家的理解,尤其是时序分析工具和理论之间的对照关系。

Data Arrival Time = Launch Edge + Tc2t + Tco + Tr2r

= 0 + 2.636 + 0.261 + (0.758-0.261)

Data Required Time = Latch Edge + Tc2r + Th

= 0 + 2.718 + 0.212

Hold time slack = Data Arrival Time – Data Required Time = 3.394 – 2.930 = 0.464ns

用户1748817 2016-4-20 17:16

用户1851850 2016-1-29 15:47

ilove314_323192455 2013-7-28 20:00

用户428627 2013-7-23 19:32

用户428408 2013-7-23 17:07

请问,如果时序不满足条件那又该如何进行操作呢?