本实例发布于《SF-CY3 FPGA套件开发指南Ver6.15 (by特权同学).pdf》中,下载地址:

http://pan.baidu.com/share/link?shareid=1370802231&uk=2184597051

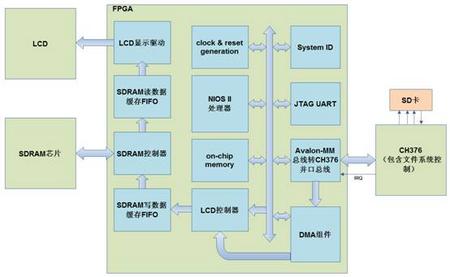

如图所示,我们这一个实例要在上一个工程的基础上,添加一个DMA组件。这个DMA组件挂在Avalon-MM总线上,用于NIOS II处理器进行一些寄存器的读写,从而完成基本的组件控制功能;而DMA组件最核心的功能,当然是搬数据了,并且是在处理器不干涉的情况下,进行数据的搬运,它从某种意义上能够大大缓解处理器的运行负荷。对于我们这个设计,这个DMA组件完全是定制化的,咱自己用代码写,而功能也很专一,就是将CH376芯片的有效图片数据直接搬运到LCD控制器端进行缓存。如此一来,就不再需要上一个实例中那样让处理器读出CH376的图片数据,再写到LCD控制器端了。一般来说,这样一来通常是能够大大提升系统性能的。只不过,我们这个系统的速度瓶颈还是在于CH376的SD读写速度,所以和上一个实例相比,这个工程无法带来非常明显的性能提升。但是没有关系,我们的重点在于DMA组件的设计,希望大家能够focus到这个点上。

关于DMA,特权同学收录在《深入浅出玩转FPGA 第二版》中的文章《DMA无处不在》,有较深入的介绍,大家不妨去看看。

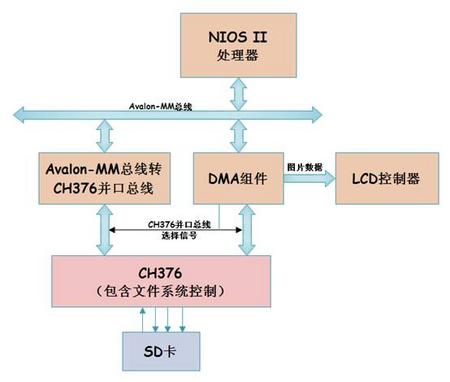

在我们的系统中,DMA总线和周边各个组件的详细连接如图所示。连接到Avalon-MM总线作为从机,这条总线由片选信号、写选通信号(主机处理器写入)、16bit写数据总线、2bit地址总线和从机中断信号组成。这条总线不直接传输图片数据,而是用于处理器完成DMA组件的各个控制功能。如下表所示,Avalon-MM总线对应操作的4个寄存器功能。

|

地址 |

有效位 |

描述 |

|

0 |

Bit1-0 |

Bit1: dma_lcd_sel – 该寄存器用于选择LCD图片数据传输是NIOS II方式(上一个实例的方式)还是DMA方式。为1时表示DMA方式,为0时表示NIOS II方式。 Bit0: dma_usb_sel – 该寄存器用于选择CH376总线的控制是NIOS II方式还是DMA方式。为1时表示DMA方式,为0时表示NIOS II方式。 |

|

1 |

Bit13-0 |

dma_wraddr – DMA方式写数据到LCD控制器端的页地址寄存器,会自动递增。 |

|

2 |

Bit7-0 |

dma_dbnum – 本次DMA传输数据字节数,取值可以是1-255。 irq_enable – 在写该寄存器时,自动开启DMA的中断使能位。 |

|

3 |

Bit0 |

irq_enable – 清除当前DMA中断使能位。 |

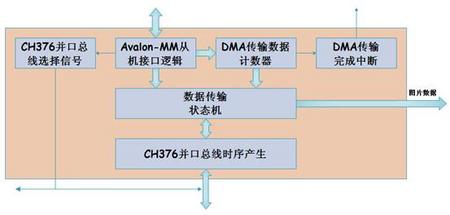

深入DMA组件内部,我们来看它的各个逻辑接口是如何设计的。如图所示,Avalon-MM从机接收到的各个控制信号相互协作,完成数据的收发中转。数据传输状态机在DMA功能启动并且DMA传输数据计数器的值不为零的情况下,将产生376并口总线时序读取当前的有效图片数据,并且产生后端FIFO(后端模块sdfifo_ctrl.v)写入数据所需的信号。而后端的FIFO在每满160个Byte后便产生一次SDRAM的页写操作,每次操作完成就会返回一个应答信号给我们的DMA组件,从而递增Avalon-MM总线可写入的页寄存器(地址1)。

另外,这里大家要注意,CH376的并口总线虽然在DMA操作时处于DMA控制状态,但并非所有的CH376指令都是由DMA组件产生,这些指令还是和上一个实例一样由NIOS II处理器产生,DMA组件只进行读数据的时序产生和控制。其实这是一个很典型的软硬件分工协同设计划分,把复杂的控制交给软件,把高重复性高速率要求的任务交给硬件来实现。

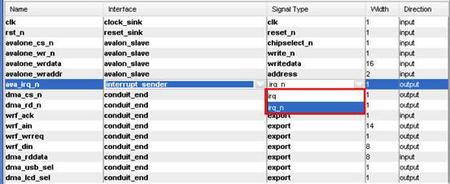

这里,我们还想对Avalon-MM从机的中断信号做一些扩展说明。如图所示,从机产生的interrupt信号可以是高电平有效(irq),也可以是低电平有效(irq_n)。如我们选择的是低电平有效,那么就意味着我们的这个中断信号在一般情况下都应该保持高电平,而一旦跳变为低电平后,保持若干时间则NIOS II处理器就能够检测到从机发送来的这个中断信号,若是这个中断信号在软件编程时使能了,并且进行了中断函数注册,那么此时NIOS II软件就会进入中断函数执行相应的处理。

对于从机而言,我们产生一个中断后,如果这个中断一直保持在低电平,不拉高,那么NIOS II处理器就会发生一些异常,可能会一直不断的进出中断函数,这是我们不想看到的。怎么办?好解决,正如我们这个组件中若对地址3写数据0x0,则关闭DMA组件的中断功能,那么久可以清除这个被拉低的中断信号,从而确保正常的软件继续工作。

/4

/4

用户377235 2013-12-18 10:27