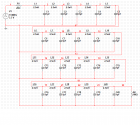

做 PCB 的,经常会遇到设计规则中等长、阻抗匹配的事情。还有传输线理论,提到信号反射等等问题。基本上会弄得一头雾水。 如果是做单片机的,根本不需要考虑这些问题。原理图上画的线,只要能连上就好。不会有什么问题。 如果设计中信号频率达到几百 M 上 GHz ,则需要考虑将信号线布线的电气参数影响因素考虑进去。电路板上的连线电气特性有三要素:电阻、电感、和电容。通常连线上的电阻对信号影响很小,可以不考虑进去。如果保持线路一致性,则信号线可以简化为多级电感电容级连的形式。需要注意的是,信号源的内阻不可能为 0 。信号源通过线路到达接收方的电路可以模拟如图:其中 R1 为信号源输出阻抗, R2 为接收端输入阻抗。 线路中电感量 L 为 2.5nH ,电容量 C 为 1pF , L/C 的平方根为 50 。 每个 L C 级的输出,可以视为下一 LC 级的输入。同样可以列出微分方程。这样可以形成一个一阶微分方程组。求解这个方程组,可以得到最后一级的输出与输入信号之间的对应关系。 也可以通过仿真,可以得到如下结果。 图中标记有 20 50 80 100 是改变 R1 (信号源输出阻抗)的阻值,得到 R2 (接收端)电压变化。 接收端信号与信号源相比, 1 、有延迟。信号源输出电阻越小,输出延迟越小。 2 、有过冲或下陷,信号源输出电阻越小,则过冲越大。当 R 等于 L/C 的平方根时。信号源上升沿与接收端的电压时间上一致。 如果将负载的输入阻抗 改为 50 Ω。 输出信号也能很好的跟踪信号源,但信号幅度会按比例变小。 从上面这些仿真(计算)结果,可以推测出高速布线的一些规则背后的理论支持。 1、 等长布线规则 信号在线路上传输都会有延迟,延迟的数据跟线长( LC 级数)有关,同步设计中,需要让时钟线与数据线的延迟一致,使数据传送或采样时处于最有利的时刻。 2、 阻抗布线规则 需要让布线的 L/C 达到一个确定的数值。让线路有准确的时间特性。 3、 源端匹配规则 需要让信号源的输出阻抗等于线路的特征阻抗(特征阻抗指的是 L/C 的均方根,具有电阻的量纲,但并不是电阻),这样输出的信号具有与信号源接近相同的时间特性。例如: SDRAM 上驱动信号(时钟,数据线,地址线等)的输出阻抗 20 Ω左右,在线路板源端串 20~30 Ω的电阻,将信号源的输出阻抗调整为接近 50 Ω,达到匹配。 4、 终端匹配规则 也可以使用终端匹配,只是会增加功耗,并且得到的信号幅度会降低。 另外,线路板上的 L C 取决于线路板材质,其中材质的介电常数最为关键,磁导率通常不会有影响。 在通常的解释中,当阻抗不匹配时,会产生信号反射。基于能量守衡的基本原则,源端的能量如果不能完全被终端接收,则能量多余的部会反射回源端。 ( 待续 )

标签: 高速信号

标签: 高速信号