AD9633在旁路SPI接口时如何在FPGA逻辑中确认字边界 概述 AD9633与FPGA之间的LVDS接口初调试,ADC可以通过SPI接口对其内部寄存器进行各项配置。在SPI接口未调通之前,对LVDS接口初步尝试调试,且已经打通。 在打通LVDS接口的基础上,FPGA收到AD采样结果后,字边界对齐是首要任务。未打通SPI接口的情况,只能使用默认配置进行调试,即在关闭SPI的时候,ADC输出总线也可以强制对外输出识别码(Pattern Code),FPGA收到此码后,即可利用LVDS的Bitslip功能完成字边界对齐。本文即记录此调试过程。 AD9633如何在未打通SPI接口时发送识别码 根据数据手册描述,在禁用SPI接口模式下,CSB直接接AVDD,这样SDIO/OLM引脚依据图1所示表格选择AD输出模式。本系统100MHz@12-bit,所以必然选择2个Lane(目前市面ADC单通道串行输出最高限速1Gbps,100MHz@12bit要单通道输出,则速率高达1.2Gbps)。 图1:输出分道模式(Output Lane Mode)引脚设置 由上确定了CSB和SDIO/OLM两个引脚的接法,下面确定SCLK的接法。SCLK/DTP引脚在禁止用SPI接口模式下用来控制AD的输出模式,即控制输出识别码还是模数转换的数值。 CSB与SDIO/OLM在上述配置的情况下,SCLK/DTP如果接AVDD,则ADC通道对外输出固定的数字识别码,即二进制的“1000 0000 0000”,即或十六进制的x“800”。具体控制如图2所示,所以切换到正常操作时,将该引脚悬空即可,实际板级设计可以使用拨码来完成图2中两个模式之间的切换。 图2:数字测试识别引脚设置 FPGA逻辑使用识别码 FPGA逻辑收到识别码,即十六进制h’800,其后实际得到数字码会发生移位,如图3所示,实际两个ADC分别接收到的是h'400和h'100,即字边界未对齐。 图3:FPGA的LVDS-RX收到的识别码解串后发生位移 如图3所示,板子上有2片不同的AD9633,均被控制发送十六进制h’800识别码,但是两个ADC均发生了位移,而且位移还不一样。 此时可以根据上图收到的实际数码,编码字边界对齐控制逻辑,让LVDS-RX模块自动完成字对齐。如图4所示,由逻辑生成控制脉冲,然后得到图5所示的控制结果,识别码从h’400到h’800的逐次转变对齐。 图4:控制逻辑产生bitslip控制脉冲提供给LVDS的rx_bitslip_ctrl端口 图5:LVDS收到bitslip脉冲后自动完成字边界对齐 注意事项 在找字边界调试的时候,发现有几个事项需要注意。首先,对于LVDS-RX模块来说,对应每个AD9633在双分道(Lane)的时候,总共有8个LVDS接收通道,所以图4中的rx_bitslip_ctrl端口有8个比特。而在调试的时候通过SignalTap观察仅有最低位能收到bitslip脉冲(如图6),似乎LSB单个bit的控制脉冲完成整个8通道的控制,而且8个通道来自同一ADC,所以其位移也是一样的,这样也不会有问题。 其次,由于ADC输出使用双Lane模式,所以12-bit分成了两个6-bit部分。所以识别码h’800也要分成两部分,所以其位移的可能性总共只有5种,即从十六进制的“800”到“400”、“200”、“100”、“080”以及最后的“040”,不会出现其余可能。 图6:Bitslip控制过程观察 参考 Quad, 12-Bit, 80 MSPS/105 MSPS/125 MSPS, Serial LVDS 1.8 V ADC Datasheet LVDS SERDES Intel FPGA IP User Guide: Intel Arria 10 and Intel Cyclone 10 Devices.

标签: lvds

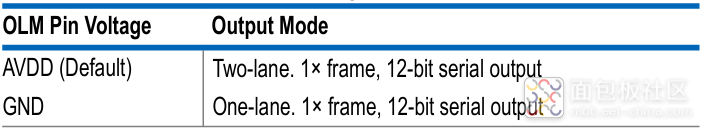

标签: lvds