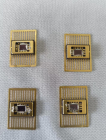

低温 烧结银的三个误区 随着新能源车和配套产业的大力发展,大功率器件封装得到了快速的发展,而大功率器件的散热问题被提升到了日程上来。 大功率散热包括芯片封装和基座的散热两部分,原来的锡膏焊接工艺由于导热系数低,不能满足大功率器件的散需求;焊膏和金锡焊片价格太昂贵得不到大面积得推广和使用,并且导热系数也不高;铟片的导热系数也不是太高。寻找高可靠高导热的材料就成为当务之急。 低温烧结银由于具备低温烧结,高导热,高可靠性,高温服役等特点被推到了台前。 但是中国市面上的低温烧结银产品鱼龙混杂,希望选择低温烧结银的朋友和客户能睁大您的火眼金睛,区别真伪,辨别真假。 AS9385烧结银 现在笔者去伪存真,提供一些参考供各位参详; 一 网页上宣传电阻到达1.6uΩ.cm的一定是不懂银的特性的企业。因为纯银的电阻是1.65uΩ.cm。更不要提他们能开发出烧结银产品了。 现在把某企业的宣传资料截图如下 电阻率μΩ·cm 2 5 1.6 二 号称可以提供烧结银全面解决方案的企业大家也要注意: 一个企业号称既能把烧结银做好又能把烧结银设备做好的企业我在全球范围内都看不到,更不要说中国的企业能把两者做好。即便是SHAREX成立6年,也是只专注低温烧结银材料,因为我们遵循:专注--专业--专家的企业理念。 当然,我们也只是善意的提醒,不信者可以自行尝试。记得今年中秋节前接到一个**单位的客户王总的电话,说在网上看到深圳某公司很厉害,既能做烧结银又能做烧结银设备,结果快递到深州某公司的样品,表面镀银的产品用了那家公司的烧结银,竟然粘结力很低, 用手稍微一碰就能脱落。后来通过朋友介绍找到我们公司,快递给我们他们公司的样品,我们做了样品给客户,测试下来符合客户的需求。 AS9120纳米银浆 三 在网上号称服务中国大部分央企的企业更是瞎扯。 因为我们服务过一家央企,把服务经验分享给大家:在2020年9月开始接触这家单位,中间沟通客户的各种具体需求和测试标准大概花了三个月的时间。根据客户的需求我们定向给客户开发了AS9330低温烧结银。 于2021年3月拿出产品让客户测试,由于AS9330低温烧结银是专门给客户订制的产品,中间客户又提出了170度以内烧结银的苛刻要求,这是全球烧结银没有做到过的烧结银温度,我们不得不又重新设计配方和二次开发,在2021年7月开发出新的配方让客户测试。开发期间客户又提出要160度以内烧结温度,我们不得不又重新设计配方,中间又赶上上海疫情严重,项目一直拖到2022年的6月份重新给客户送样测试。 网上看到一个搞笑的企业,成立于2021年,已经服务各大企业了,我们只能说这家企业厉害的不要不要的,我们自叹弗如。 AS9330烧结银

标签: 芯片封装

标签: 芯片封装