引言 碳化硅(SiC)作为新一代半导体材料,因其卓越的物理和化学性能,在功率电子、高频通信、高温环境等领域展现出巨大的应用潜力。然而,在SiC外延片的制备过程中,常常会遇到外延层不合格的情况,这时就需要将外延层去除,然后利用剩余的衬底进行再生处理,以降低生产成本并提高材料利用率。本文将详细介绍一种碳化硅外延片去除外延再生衬底的方法,该方法结合了高效的去除技术和精细的再生处理步骤,旨在实现不合格外延片的再利用。 方法概述 碳化硅外延片去除外延再生衬底的方法主要包括以下步骤:测量与评估、外延层去除、衬底再生处理以及化学机械抛光(CMP)。每个步骤都经过精心设计和优化,以确保最佳的去除效果和再生质量。 测量与评估 测量外延片参数:使用表面厚度测量仪测量外延层上多个点的厚度,得到厚度值hi(i=1,2,...n),n为大于等于1的正整数。同时,使用表面平整度测量仪测量外延片的总厚度H以及其平整度最大值TTV.MAX,平整度最大值是指衬底的生长外延层的侧面上的最高位置与最低位置之间的高度差。 评估外延层质量:根据测量的厚度和平整度数据,评估外延层的质量。对于不合格的外延层,需要进行去除处理。 外延层去除 减薄处理:根据外延平均厚度,使用双轴减薄机对外延层进行减薄处理。双轴减薄机采用金刚石和树脂等加工而成的砂轮,在高速旋转下对外延片的表面进行快速切削,以实现高效的去除效果。减薄处理包括第一减薄处理和第二减薄处理,可以根据需要选择使用粗砂轮或细砂轮。 冲刷清洗:减薄处理后,使用双面刷洗机对外延片的两面进行冲刷清洗,以去除残留的切削屑和杂质。冲刷清洗过程中,使用尼龙毛刷和二流体(如纯水和氮气)进行反复冲刷,确保外延片表面的清洁度。 衬底再生处理 计算衬底厚度:根据外延片的总厚度和减薄厚度,计算衬底的厚度。衬底的厚度等于外延片的总厚度减去减薄厚度。 检查衬底质量:对再生后的衬底进行质量检查,确保无裂纹、无杂质等缺陷。对于质量不合格的衬底,需要进行进一步的处理或更换。 化学机械抛光(CMP) 抛光处理:将经过冲刷清洗并符合质量要求的多个外延片贴于化学机械抛光设备的陶瓷盘上,然后对这些外延片同时进行至少一次化学机械抛光处理。CMP技术是外延片抛光中的最后一道工艺,通过抛光液和抛光垫的相互作用,将外延片表面的损伤层去除,从而降低表面粗糙度。 质量检查:抛光处理后,对外延片进行质量检查,确保表面平整度、粗糙度和洁净度等指标满足要求。 技术优势 高效去除:该方法采用双轴减薄机进行外延层的去除,具有高效、精确的去除效果,能够显著提高去除效率和质量。 精细再生:通过精细的再生处理步骤,包括冲刷清洗、计算衬底厚度和CMP抛光等,能够实现不合格外延片的再生利用,降低生产成本。 提高材料利用率:该方法将不合格的外延层去除后,利用剩余的衬底进行再生处理,显著提高了材料的利用率,有助于推动碳化硅半导体材料的商业化发展。 应用前景 碳化硅外延片去除外延再生衬底的方法在SiC半导体材料制备领域具有广阔的应用前景。随着SiC半导体技术的不断发展,对高质量、高性能的SiC外延片的需求日益增长。通过采用该方法,可以显著降低SiC外延片的制备成本,提高材料利用率,为制造高性能、高可靠性的SiC器件提供有力支持。此外,该方法还适用于其他半导体材料的外延片制备过程,具有广泛的适用性和推广价值。 结论 综上所述,碳化硅外延片去除外延再生衬底的方法是一种高效、精确的去除和再生处理技术,能够实现不合格外延片的再利用,降低生产成本并提高材料利用率。该方法在SiC半导体材料制备领域具有重要的应用价值,有助于推动SiC半导体技术的商业化发展。未来,随着SiC半导体技术的不断进步和应用领域的拓展,该方法将发挥更加重要的作用。 高通量晶圆测厚系统 高通量晶圆测厚系统以光学相干层析成像原理,可解决晶圆/晶片厚度TTV(Total Thickness Variation,总厚度偏差)、BOW(弯曲度)、WARP(翘曲度),TIR(Total Indicated Reading 总指示读数,STIR(Site Total Indicated Reading 局部总指示读数),LTV(Local Thickness Variation 局部厚度偏差)等这类技术指标。 高通量晶圆测厚系统,全新采用的第三代可调谐扫频激光技术,相比传统上下双探头对射扫描方式;可一次性测量所有平面度及厚度参数。 1,灵活适用更复杂的材料,从轻掺到重掺P型硅(P++),碳化硅,蓝宝石,玻璃,铌酸锂等晶圆材料。 重掺型硅(强吸收晶圆的前后表面探测) 粗糙的晶圆表面,(点扫描的第三代扫频激光,相比靠光谱探测方案,不易受到光谱中相邻单位的串扰噪声影响,因而对测量粗糙表面晶圆) 低反射的碳化硅(SiC)和铌酸锂(LiNbO3);(通过对偏振效应的补偿,加强对低反射晶圆表面测量的信噪比) 绝缘体上硅(SOI)和MEMS,可同时测量多层结构,厚度可从μm级到数百μm级不等。 可用于测量各类薄膜厚度,厚度最薄可低至4μm,精度可达1nm。 2,可调谐扫频激光的“温漂”处理能力,体现在极端工作环境中抗干扰能力强,充分提高重复性测量能力。 3,采用第三代高速扫频可调谐激光器,一改过去传统SLD宽频低相干光源的干涉模式,解决了由于相干长度短,而重度依赖“主动式减震平台”的情况。卓越的抗干扰,实现小型化设计,同时也可兼容匹配EFEM系统实现产线自动化集成测量。 4,灵活的运动控制方式,可兼容2英寸到12英寸方片和圆片测量。

标签: sic

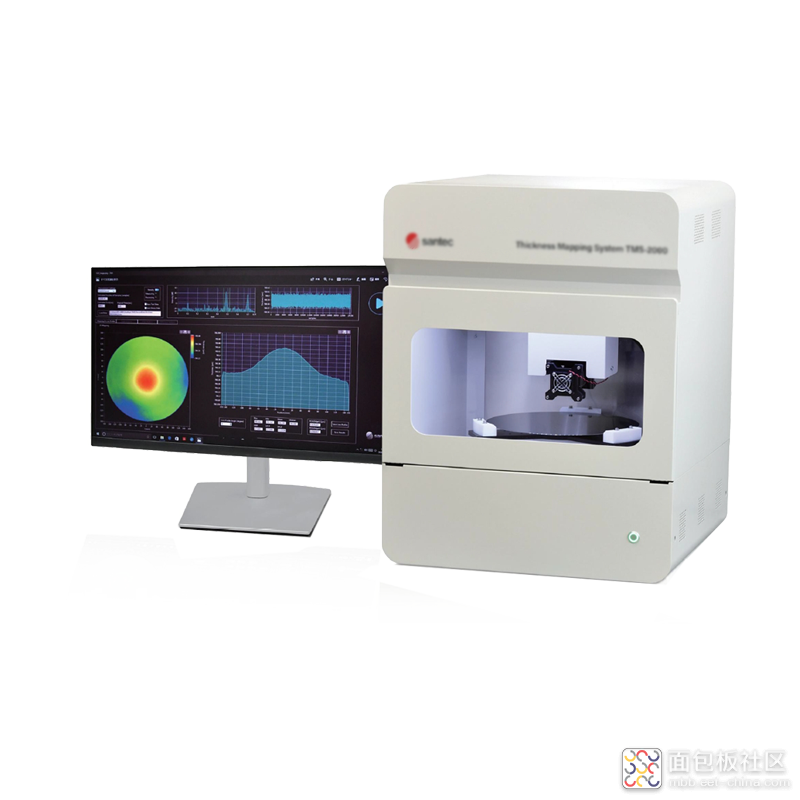

标签: sic