使用ALTERA专用时钟控制模块消除时钟问题

概述

时钟处理不当很容易引起不必要的时序问题,本文通过一个简单的例子来展示FPGA内部出现极端时钟歪斜导致的时序问题,以及解决方法。

问题简单描述

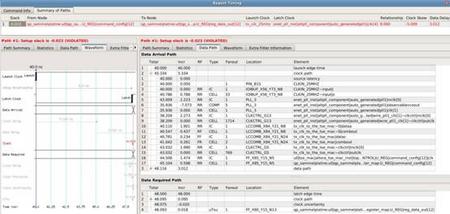

在三速以太网应用中需要根据不同条件选择系统时钟,所以需要一个时钟多路选择器。假如时钟多路选择器使用图1所示的简单架构,那么设计编译得到了如图2所示的时序结果。

图1:时钟多路选择器设计方案一

图2:时钟多路选择方案一导致的时序问题

很明显,时钟多路选择器输出的时钟并没有使用专用的时钟布线资源。我们来看这个时钟多路选择器在代码中的具体实现:

tx_clk_to_the_tse_mac <= enet_clk_125mhz when('1' = eth_mode_from_the_tse_mac) else -- GbE Mode = 125MHz clock

enet_clk_2p5mhz when('1' = ena_10_from_the_tse_mac) else -- 10Mb Mode = 2.5MHz clock

enet_clk_25mhz; -- 100Mb Mode = 25MHz clock

方案优化

分析时序报告结果,既然确定是多路选择输出的时钟没有走时钟专用布线资源,那么就需要对该时钟进行约束,或者更改原始设计。我们选择修改代码设计,代码修改如下所示:

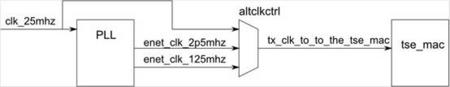

blk_enet_clkctrl: block signal enet_clkctrl_cs : std_logic_vector(1 downto 0) := (others => '0'); begin enet_clkctrl_cs <= "10" when ('1' = eth_mode_from_the_tse_mac) else "11" when ('1' = ena_10_from_the_tse_mac) else "00"; inst_enet_clkctrl: component enet_clkctrl PORT MAP ( clkselect => enet_clkctrl_cs, inclk0x => CLKIN_25MHZ, inclk1x => '0', inclk2x => enet_clk_125mhz, inclk3x => enet_clk_2p5mhz, outclk => tx_clk_to_the_tse_mac ); end block;这里我们使用了Altera专用时钟控制模块,该模块可以保证其输出自动布线到全局资源上。上述代码的架构如图3所示。

图3:时钟多路选择器优化方案

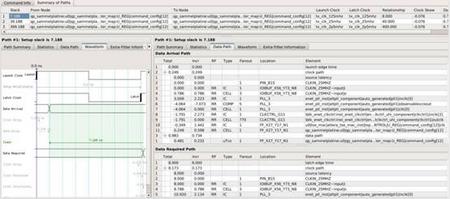

这样tse_mac模块的输入时钟上的抖动降低到最小,如图4所示。同时将收发路径设置false paths以及根据ALTERA推荐对时钟控制进行相关设置,最终时序也就能达到预期要求。

图4:优化后的时序分析报告

/5

/5

文章评论(0条评论)

登录后参与讨论