高速差分IO评估(LVDS)

概述

很多人在使用ALTERA的高速差分接口,即LVDS,老是遇到问题,作为参考笔者基于Altera的Stratix II器件评估其LVDS接口。Altera的高端器件的LVDS接口集成了专用的硬件资源,而且逻辑设计的时候可以直接调用LVDS设计模块。相对于低端的Cyclone系列,用户在使用的时候需要投入更多的精力。

学习目标

l 创建高速差分接口LVDS发送和接收器

l 学习如何分配高速差分I/O

l 使用片上自带的匹配电阻(Cyclone系列没有)

l 使用ModelSim仿真LVDS接口

开始进行专用高速差分I/O设计

如图1所示,我将要在StratixII器件上实现如下的设计。该设计利用器件专用的SERDES高速差分I/O运行在840 Mbps。接收器的两个8-bit输出使用内部的专用乘法器相乘,相乘的结果送入LVDS发送器。下面我们开始使用Megawizard来创建两个通道的LVDS Rx和Tx设计文件以及顶层文件。

图1:LVDS高速差分设计实例

第一步:创建LVDS接收器

使用Megawizard生成LVDS接收器,速率为840 Mbps,时钟为105 MHz,X8模式。

1、 首先创建一个Quartus II工程,命名为Diff_io_top.qpf,并打开此工程。

2、 从工程的工具菜单选择Tools à MegaWizard Plug-In Manager。在弹出的插件管理器界面选择Create a New Custom Megafunction Variation。然后点击下一步。

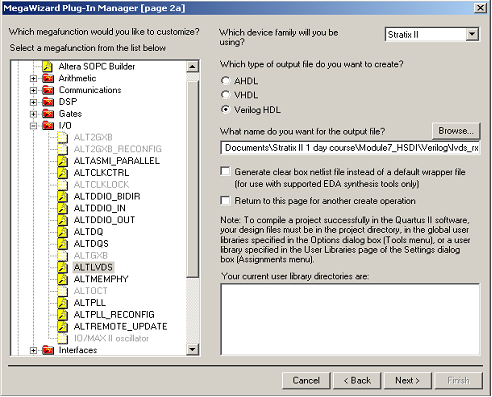

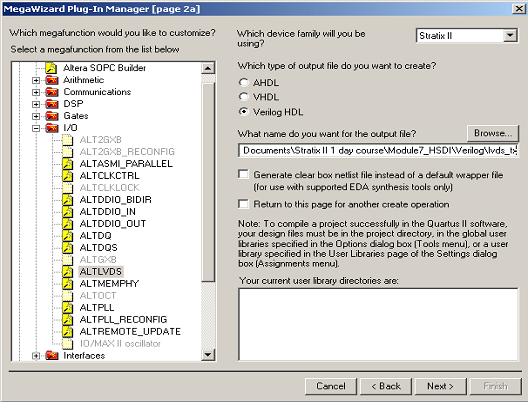

3、 在出现的界面中,展开“I/O”项并选择“ALTLVDS”。选择好生成的源文件HDL输出类型(Verilog或VHDL)并指定器件为Stratix II。输入源文件输出名字为lvds_rx,点击下一步,如图2所示。

图2:生成LVDS接收器第二页

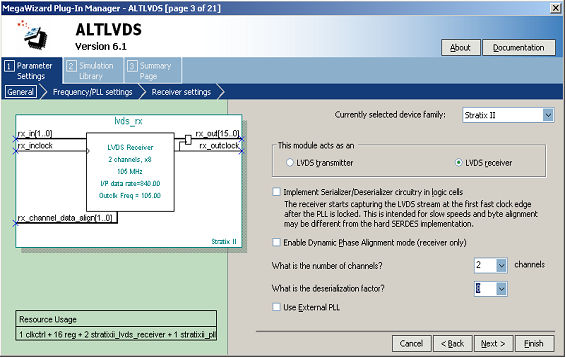

4、 在下一个窗口选择生成LVDS receiver模块。指定Stratix II作为器件家族。选择通道数为2通道。选择解串化因子为8,如图3所示。

图3:

5、 点击下一步(Next)继续

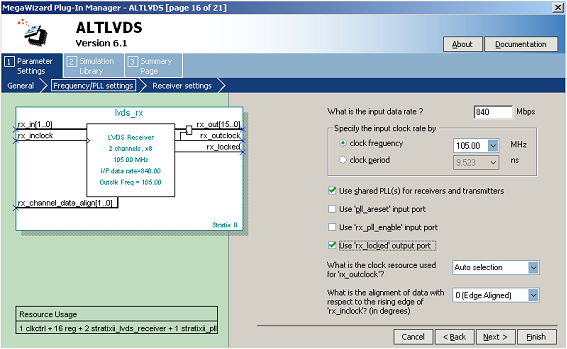

6、在接着出现的窗口中选择接口速率为840 Mbps。勾选“Use rx_locked output port”。“ alignment of data with respect to rx_inclock”默认为“EDGE_ALIGNED”。通过时钟频率来指定输入时钟速度,并指定为105 MHz。勾选“Use shared PLLs for Rx and Tx”。如图4所示。

图4:

7、 点击下一步(Next)继续。

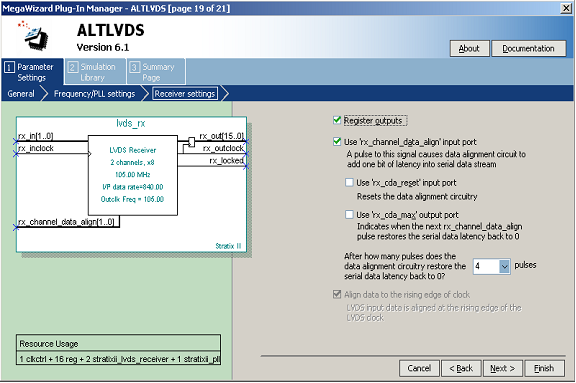

8、 在出现的窗口中勾选“Use the “rx_data_align” input port”。勾选后界面如图5所示,点击“Finish”后选择生成所有文件,并再次点击“Finish”按钮。

图5:

至此,我们已经创建了一个LVDS接收器模块,此时我们会在工程目录下得到一个lvds_rx.vhd文件。

第二步:创建LVDS发送器

和上一步一样我们再生成一个对应的LVDS发送器模块,速率840 Mbps,时钟105 MHz,X8模式。

1、 在Quartus II工程的工具菜单中选择MegaWizard插件管理器,在弹出的窗口中选择“Create a New Custom Megafunction Variation”,并点击“Next”按钮继续。

2、 在出现的窗口中展开I/O项,并从中选择ALTLVDS。同样这里选择生成VHDL输出源文件。为生成的模块命名为lvds_tx。点击Next继续,如图6所示。

图6:

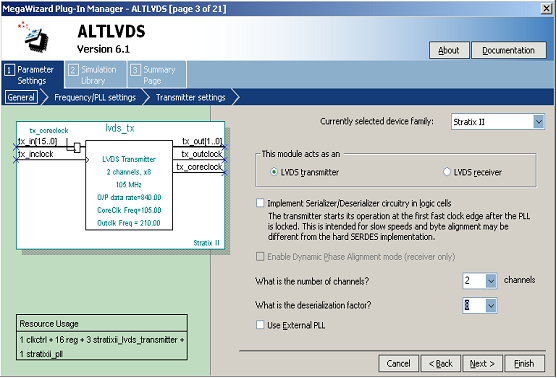

3、 在出现的窗口中,确认选择生出的是发送模块。选择Stratix II器件,修改通道数为2,修改解串因子为8,点击Next继续,如图7所示。

图7:

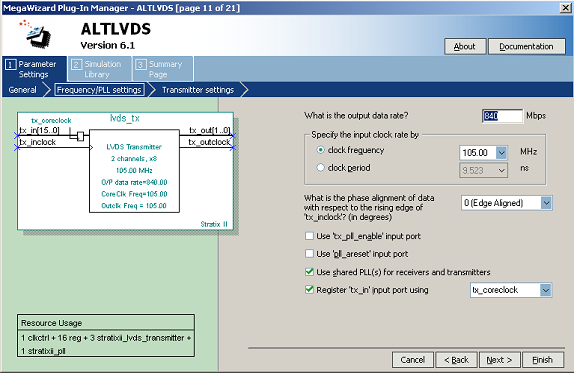

4、 在出现的窗口中,修改输出数据率为840 Mbps。在指定输入时钟速率框下勾选“clock frequency”并指定时钟速率为105 MHz。勾选“Register input”和“Use shared PLL for receiver and transmitter.”,然后点击Next继续,如图8所示。

图8:

5、 在出现的窗口中设置“outclock divide factor”为8,不要勾选“Use ‘tx_locked”output port”,并点击Finish按钮后选择生成所有文件后再次点击Finish按钮完成模块生成,如图9所示。

图9:

至此LVDS发送模块已经生成,此时我们可以在工程目录下看到生成的源文件lvds_tx.vhd。

第三步到第六步省略了

这就几步分别介绍了:

l 如何在设计中例化LVDS收发模块

l 为LVDS收发模块分配输入输出LVDS标准的 I/O引脚

l 编译设计

l 检查底层布局布线

l

第七步 使用ModelSim对LVDS模块进行仿真

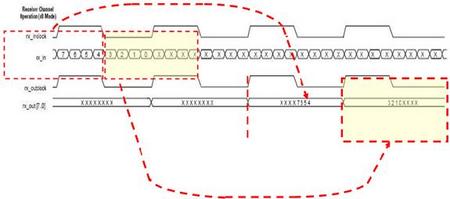

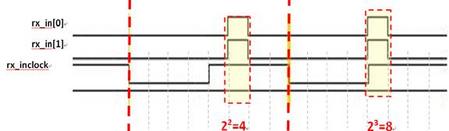

在我们进行仿真之前,非常有必要了解下LVDS高速接口中的数据帧格式。上面我们各创建了2对LVDS收发通路,串化因子为8,这意味着高速串行通道在每个rx-inclock周期内传输一组8-bit的数据。在接收端,8-bit字边界由接收器时钟的下降沿来确定,如图10所示,每个时钟周期给FPGA逻辑发送一个8-bit数据。

图10:串化因子为8时的解串方式

根据图10那么我们来看图11给出的例子,图中与时钟下降沿对齐的两个字节的数据,应该分别是数值4和8,因为每个时钟周期内,rx_in上的只有一个bit为‘1’,且分别位于bit2和bit3的位置。

图11:接收端串行数据解串举例

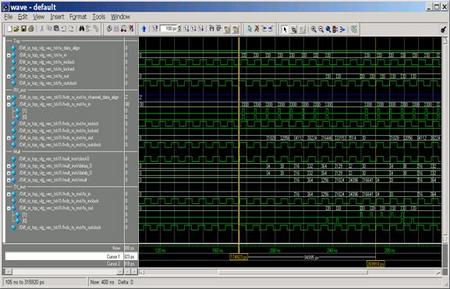

下面开始使用ModelSim对LVDS模块设计进行仿真,这里我们采用自动化仿真方式。建立批处理文件、脚本文件(sim.do和wave.do),当然最重要的是是设计合适的测试激励文件。这些文件都以附件的形式给出,这里不做过多解释,图12显示了仿真的最终结果。

图12:LVDS仿真结果

这里对于仿真的过程不再过多赘述,博主前面有详细的博文介绍,本文附件里也给出了详细的仿真工程,大家除了可以直接拿来仿真lvds以外,最重要的是理解仿真工程里的相关lvds的测试激励。

/5

/5

用户1208903 2015-5-4 10:22

用户1828471 2015-5-2 18:06

用户1661642 2008-4-15 15:40

用户1053025 2006-11-20 15:31