概述

Cyclone 10 GX器件的ALM结构与Cyclone V类似,所以在Cyclone 10 GX器件上实现TDC功能理论上是可以完全参考甚至移植自Cyclone V系列的成功案例。但是,现实却是更多的问题出现当在Cyclone 10 GX使用和Cyclone V同样策略实现TDC的时候。

本文主要记录在Cyclone 10 GX器件上实现TDC时的探索,并为后续TDC设计、测试等展开前期研究。

Cyclone 10 GX ALM结构

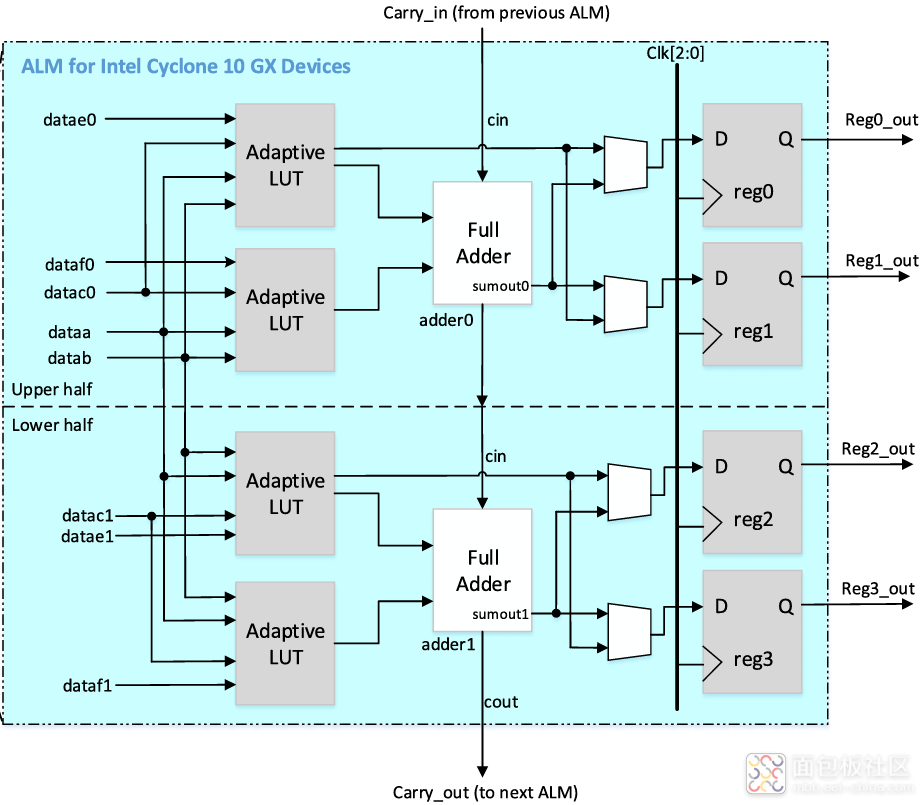

如图1所示,Cyclone 10 GX器件的ALM结构延续自Stratix II,只是从5代开始,每个ALM中的寄存器从2个增加到4个。

图1:Cyclone 10 GX ALM内部结构

如图1所示,使用进位链可以实现所需长度的TDL,每级进位链的Sumout?则可以通过ALM内的寄存器TAP输出。以前进位链单元与寄存器时1:1对应,图1中进位单元与寄存器的比例是1:2的关系。这使得用户在进行TDC设计的时候,可以利用该比例关系,获得双倍的TAP输出码元,从而在使用同样的进位资源的情况下获得双倍的TDC精度。笔者称此方法为双寄存(Dual Reg)方法,而之前方法对应为单寄存(Single Reg)方法,两种方式实现的TDL如图2所示。

图2:单寄存(Single Reg)TDL(左)与双寄存器(Dual Reg)TDL(右)

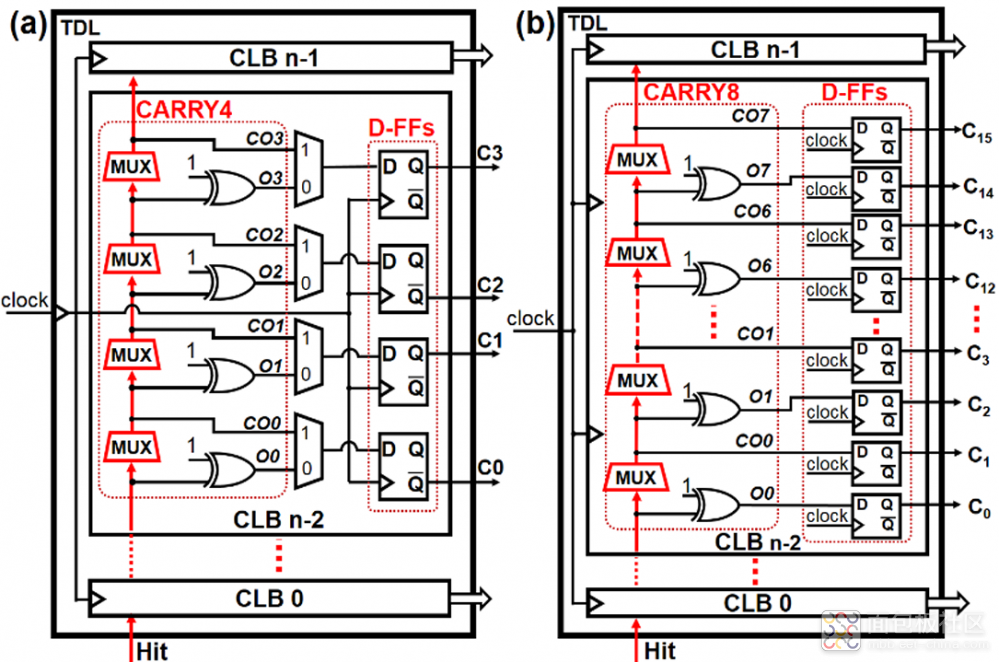

Intel ALTERA与Xilinx双寄存器的比较

已有研究者分别在Xilinx和Intel ALTERA的器件(28nm及以后)中使用了上述双寄存方法实现TDL,如果仔细研究二者的逻辑单元(CLB与ALM)的结构,可以发现进位单元到寄存器的路径还是有区别,如图3所示为Xilinx器件中进位到寄存器路径。

图3:Xilinx器件中进位到寄存器之间路径

如图3所示,和ALTERA类似,(a)为老器件的单寄存,而(b)为新器件中的双寄存,不管单寄存还是双寄存,Xilinx的进位到寄存器的路径有2条(分别为C与S,而ALTERA器件如图1所示只有S,C并未引入到寄存器),而ALTERA只有一条,所以有研究者分别探索了使用两种不同路径的效果,相关结果可以查看对应的论文,这里不在赘述。

TDC初步测试结果

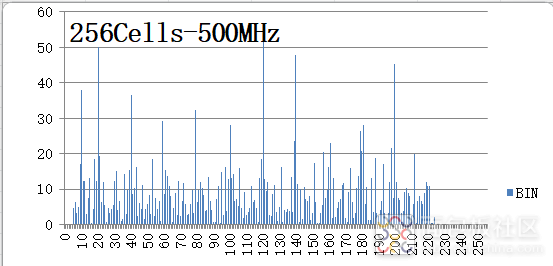

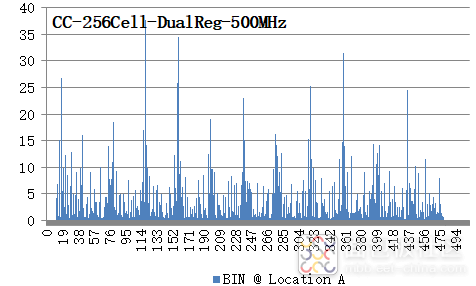

依据前期对Cyclone 10 GX的研究,以及前期在Cyclone V系列器件上对TDC实现的经验,通过直接调用进位链和寄存器原语的方式完成TDC功能完整例化实现。总共有3种不同类型的TDC得到了实现,并进行了初步的测试,TDL的Tap时钟为500MHz。三种TDC的DNL测试结果列举如下。

1、单TDL单寄存,TDL的长度为256,足够覆盖2ns的时钟周期

图4:256 cells的TAP输出单寄存器阵列锁存(8-bit细时间,LSBav=8.9ps)

2、单TDL双寄存

图5:256 cells的TAP输出双寄存器阵列锁存(9-bit细时间,LSBav=4.3ps)

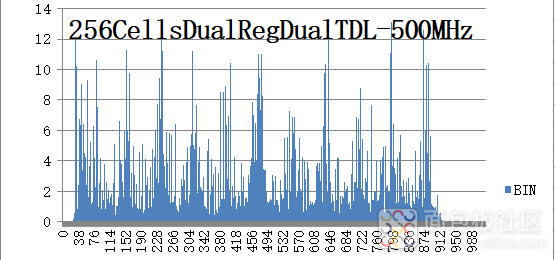

3、双TDL双寄存

图6:双256 cells TDL链的TAP输出双寄存器阵列锁存,然后合并(10-bit细时间,LSBav=2.2ps)

参考

[1] Cyclone 10 GX FPGA Handbook

[2] “LCELL WYSIWYG Description for the Cyclone II Architecture,” p. 13, 2005. [Online]. Available: https://community.intel.com/t5/ Intel-Quartus-Prime-Software/Designing-with-low-level-primitives/ td-p/110485?profile.language=en&attachment-id=30610

作者: coyoo, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1010859.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

文章评论(0条评论)

登录后参与讨论