概述

新的数据处理板融合了数字和数据处理功能模块,计划采用ADI的4通道串行ADC芯片代替之前的并行ADC。由于初次使用,所以初次设计时预留了AD9218的子板的插槽。

在调试AD9633功能的同时并不影响SiPM读出测试系统的联调,只是在新处理板上使用AD9218子板的时候出现了意料之外的问题。本文就该问题展开分析。

新的处理板架构其实非常简单,就是将之前分离的数字处理板和数据处理板合并一处。所谓数字处理板,主要是将前端模拟信号经过模数转换得到数字信号,并将得到的数字信号进行必要的预处理后传输到后一级的数据处理板。

而数据处理板主要功能是将接收来自数字处理板的信号进行基于单事件和符合事件两种不同的模式进行处理,并形成基于时间戳的数据流,利用DAQ接口将排好序的数据流上传给上位机。

老的结构,主要是集中数字化,即数字板集中收集前端众多模拟信号,集中进行数字化,所以单个数字处理板上集中了多个ADC(SST系统数字单板集中有40个ADC通道),整个系统又由多个数字处理板组成,这样数据处理和数字处理板之间通信经由高速背板完成。

新的结构,将数字处理结构打散,并尽量向前布置。即单个模块可以分别单独数字化,然后数据再下传。AD9633集成了四个ADC通道,可以很好完成单个模块四个模拟信号(ABCD)的数字化。ADC和前端驱动芯片和SiPM读出测试模块可以绑定一起组成更大的模块,然后形成更为集中的前端处理模组。

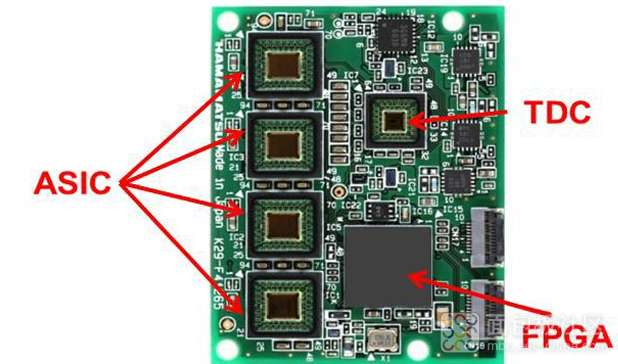

AD9218集成了2个通道,理论上也可以完成上述集成,只是其采样输出为并行结构,这样需要更多的数据总线传输数据,而且长距离传输不利于数据传输稳定。而AD9633的输出总线为LVDS差分对结构,很好解决了此问题。图1为滨松公司为用户提供的开发套件中关键的前端信号处理板。

我们新的信号处理板为了验证前端数字和后端数据处理,将前端数字和后端数据处理融合一起,而图1中的ASIC模块功能,则由独立的SiPM读出测试系统完成。这就是目前新处理板即便架构,该机构保留了AD9218和AD9633两种数字处理模块,二者并行相互独立。

图1:滨松开发套件中的前端信号处理板

AD9218子板在新处理板上遇到的问题

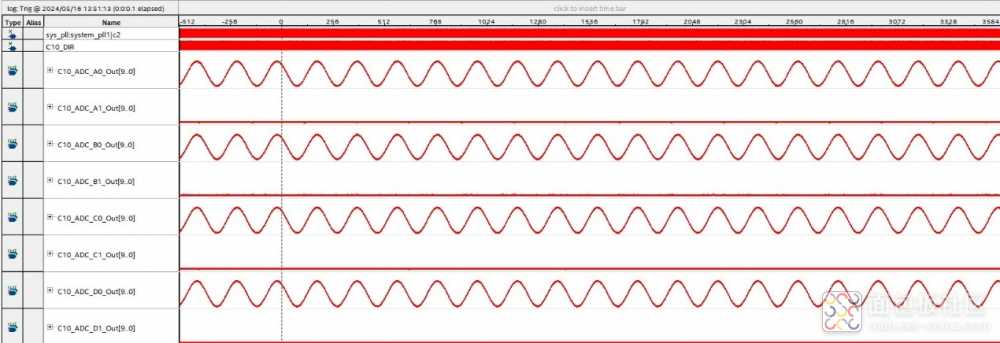

因为AD9218是预制的子板,而且在前一代系统经过验证可以正常使用,所以该问题必然是由此处理板引起。如图2所示,为AD9218正常工作表现;而图3则为AD9218出现异常时状况。

图2:AD9218正常工作表现

图3:AD9218工作出现异常

新处理板为符合测试,给AD9218预留了4个槽位,即总共8个ADC通道。经过测试,发现上述问题在每个ADC通道上都会出现,ADC子板由于可以拔插,所以更换不同ADC子板后,问题依旧存在,所以如上述总结那样,此问题与ADC子板无关,其根源来自新的处理板。

AD9218输出并未直接引入FPGA(Cyclone 10 GX系列),而是经过一片MAX10 CPLD转接后送入FPGA。C10GX器件总共只有1个BANK支持3.0V的I/O标准,这不多的3V引脚都分配给了ARM和DAQ总线,并无足够的引脚用于AD9218。

MAX10器件可以使用其3V标准I/O BANK接收所有AD9218通道的输出总线,然后直通由该CPLD的其它1.8V I/O BANK输出并直接接入FPGA。CPLD与FPGA之间的I/O均为1.8V。如此很好解决了FPGA收AD9218数字输出的问题。

调试伊始,也曾怀疑上述异常是否与CPLD有关,经过测试,发现CPLD对应的接收ADC和传送ADC数据都存在上述问题,所以根源还是来自ADC与CPLD无关,而ADC问题根源与上述分析那样,来自处理板。具体应该是和板子供电有关,电源模块的相关噪声耦合到了模拟输入信号,而且这种串扰还是间隙性的偶发,不会一直存在。

参考

[1] Quad, 12-Bit, 80 MSPS/105 MSPS/125 MSPS, Serial LVDS 1.8 V ADC Datasheet

[2] LVDS SERDES Intel FPGA IP User Guide: Intel Arria 10 and Intel Cyclone 10 Devices.

作者: coyoo, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1010859.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/1

/1

ALICEWANG 2025-1-6 08:33