前几日,探长曾撰文介绍过CMOS在降低芯片功耗方面所起的关键作用,本文继续围绕芯片这个话题展开讨论,并就芯片材料这个中心议题进行深入探讨。<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

我们知道,二氧化硅在MOS器件内用于栅极隔离和硅基层材料,在器件与器件之间、器件与导线之间、导线与导线之间用作绝缘材料(填充材料)。40年以来,二氧化硅一直在芯片中担当着重任,但是,随着集成度的提高,二氧化硅已经力不从心了。

1. 栅极氧化物被高k材料取代

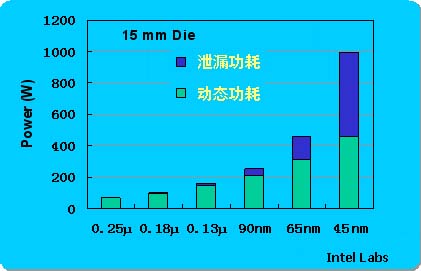

CPU功耗与供电电压的平方成正比,降低核心电压可以大大降低CPU功耗。从Intel 8086到Intel 80486,CPU的供电电压一直为5V,从Pentium开始,电压值一路下滑,直至今天的1V以下。即便这样,由于晶体管数量持续增加,CPU的总体功耗始终是制造商面临的一个严重问题,居高不下的功耗已经成为限制晶体管数量和提升频率的一道难关。

工艺尺寸缩小了,泄漏功耗增加了

MOS管作为组成IC的基本单元,也是电力的主要消耗场所。近年来,随着工艺尺寸的持续缩小,就必须尽可能把栅极做得尽可能的薄,以维持栅极氧化层有足够大的电容量,维持MOS管正常的导通和关闭功能。但是,栅极太薄了又容易出现电流泄漏。特别是在90nm技术节点,栅极氧化层(也称隔离层)的厚度只有0.9~1.4nm,导致Prescott核心功耗猛增,发热严重,提升CPU频率的努力遭遇到前所未有的困难。到了65nm这个工艺节点,隔离层厚度仅有5个氧原子的厚度了,二氧化硅已经难以担当此任了。

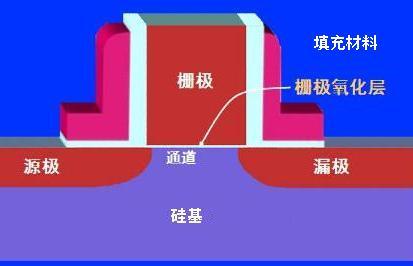

MOS管的构造,栅极氧化层的作用相当于电容

从一般意义上来说,二氧化硅是一种良好的绝缘体。但是,这种已经使用了近40年材料,在厚度减少到一定程度以后,电子就能够穿透隔离层,漏电流显著升高。这样,作为阻隔栅极与通道的绝缘体,栅极氧化层的厚度已经无法进一步缩小了。

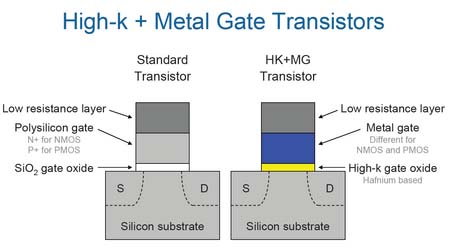

新旧两种MOS管在结构上的差异

使用高k值氧化物是为了在隔离层面积缩小的情况下厚度并不降低,栅极与通道之间的电容量也不减少。因为在同样尺寸(面积和厚度)下,电介质的k值越高,电容量越大。至于具体的高k材料,过去曾经使用过ZrO2、SiON以及Si3N4等,Intel在45nm工艺节点中采用铪(Hafnium)氧化物作为隔离层,因为这种材料与多晶硅之间兼容性不好,最终用金属门取代了多晶硅门才解决了问题。据说经过这样处理,可使电力消耗降低30%,性能提高20%。

2. 填充材料被低K电介质取代

虽然电流泄露途径主要是“门泄漏”,但“电介质泄漏”问题也同样不可忽视。芯片衬底材料以及芯片层间的绝缘材料通常采用SiO2,但因SiO2的K值较高(介电系数约为3.9~4.5)而产生较大寄生电容,带来信号串扰和感应漏电,因此,新微处理器中广泛采用CDO(碳掺杂的氧化硅)等低k材料取代SiO2。

众所周知,所有材料从导电特性上可分为导体和绝缘体两种类型,导电性能良好的材料称为电的良导体或直接称为导体,导电性能差的材料称为电的不良导体或者称作绝缘体。导体中含有许多可以自由移动的电子,而绝缘体中电子被束缚在自身所属的原子核周围或夹在原子核中间,这些电子可以相互交换位置,但是无法随处移动。绝缘体不能导电,但电场可以在其中存在,并且在电学中起着重要的作用。因此,从电场的角度,通常也称绝缘体为电介质(dielectric)。

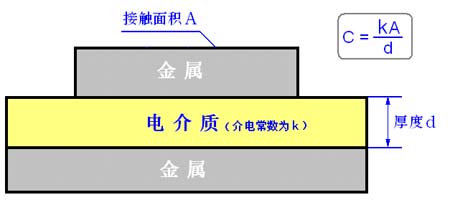

正如导体一样,电介质在电子工程领域有着广泛应用,电容器内的储电材料以及芯片内的绝缘材料等都是电介质。为了定量分析电介质的电气特性,用介电常数k(permittivity或dielectric constant)来描述电介质的储电能力。

绝缘体自身因具备储电能力,材料内部有寄生电容产生。我们知道,电容C定义为储存的电量Q与电压E的比值,在相同电压下,储存的电量越多,则说明电容器的容量越大。电容的容量与电容器的结构尺寸及电介质的k值有关,其中作为储电材料的电介质的k值对电容容量的大小起着关键性作用,制造大容量的电容器时通常是通过选择高k值的电介质来实现的。

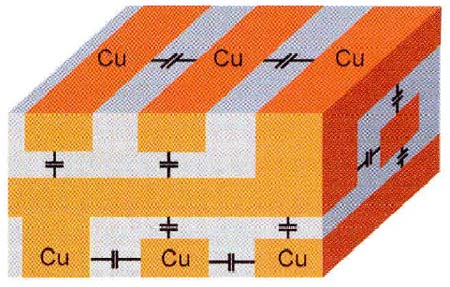

芯片内部连线之间的寄生电容

不同材料的电介质的介电常数k相差很大,真空的k值为1,在所有材料中最低;空气的k值为1.0006;橡胶的k值为2.5~3.5;纯净水的k值为81。工程上根据k值的不同,把电介质分为高k电介质和低k电介质两类。介电常数k>3.9时,称这种电介质为high-k;而通常把k≤3.9的电介质称作low-k电介质。IBM将low-k标准规定为k≤2.8,目前业界大多以2.8作为low-k电介质的k值上限。

在集成电路内部,由于ILD(Inter Layer Dielectrics,层间电介质)的存在,导线之间就不可避免地存在分布电容,或者称之为寄生电容。分布电容不仅影响芯片的速度,也对工作可靠性构成严重威胁。

从电容器容量计算公式中我们可以看出,在结构不变的情况下,减少电介质的k值,可以减小电容的容量。因此,使用低k电介质取代二氧化硅,可以有效地降低互连线之间的分布电容,从而有效提升芯片性能。

电容的定义

目前90/65nm采用的绝缘材料k值均在2.4以上,k值还不够低。IBM开发出所谓的Airgap技术,就是将导线之间的介电材料完全镂空。据IBM说,与目前最先进的芯片比较,采用Airgap技术能使信号传输速度提高35%,耗电量降低15%。IBM计划将这项技术整合到未来的32nm工艺中。

【小结】SiO2的k值约为3.9~4.5,用作栅极隔离层时k值有点儿低了,用作填充材料又嫌它有点儿高了。在对芯片材料要求越来越苛刻的情况下,低的要更低,高的要更高,而SiO2高不成低不就,不再适应时代的需要了。SiO2从芯片中消失以后,我们经常挂在嘴边“硅芯片”这个词汇也就有其名而无其事了。

/4

/4

文章评论(0条评论)

登录后参与讨论