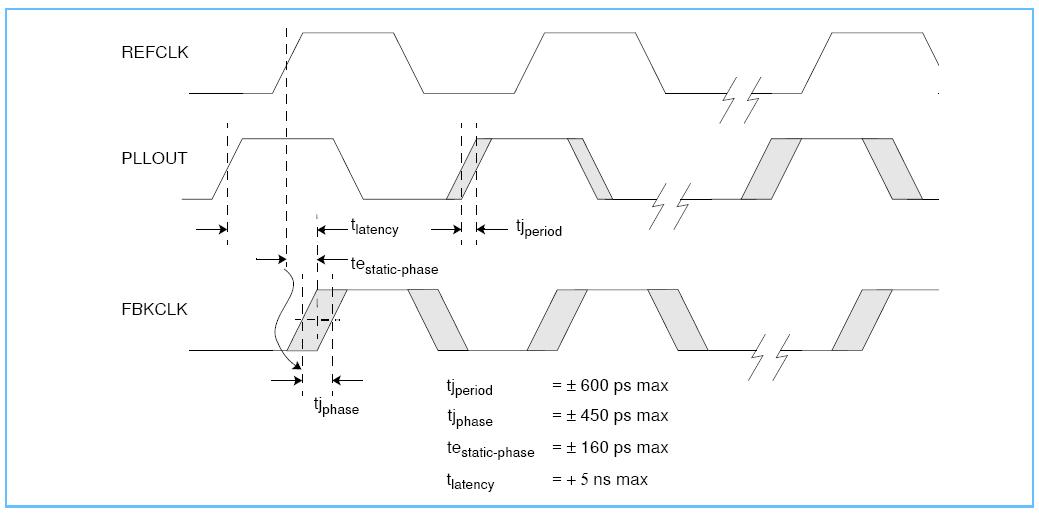

Jitter is a random variation of the output clock. It is caused primarily by AVDD/AGND and substrate noise perturbing the VCO(Voltage Controled Oscillator) within the PLL. It can also be caused by excessive jitter on the REFCLK input. Output jitter is defined in three ways: period jitter. duty-cycle jitter, and phase jitter.

时钟抖动是输出时钟的随机变化。其主要是由AVDD和AGND以及基底噪声干扰PLL中VCO引起的。其也可由参考输入时钟的较大的抖动引起。输出时钟抖动定义为三种类型:周期抖动,占空比抖动和相位抖动。

Period Jitter: refers to the deviation in cycle time of a signal with respect to the ideal period over a random sample of cycles.

周期抖动:指的是信号的周期时间的随机采样与理想周期之间的差异。

Duty-cycle Jitter: refers to the magnitude of the deviation in time duration between the primary threshold crossing and the secondary threshold crossing in a cycle over a random sample of signals.

占空比抖动:指的是随机采样一个信号的一周期中前一翻转和后一翻转之间的时间,这些采样时间的差异幅度。

Phase Jitter: refers to the deviation of the FBKCLK rising edge to the REFCLK rising edge with respect to the average offset in a random sample of cycles.

相位抖动:指的是反馈时钟和参考时钟之间上升沿差异与多次随机采样的平均偏移之间的差。

/5

/5

文章评论(0条评论)

登录后参与讨论