术语解释

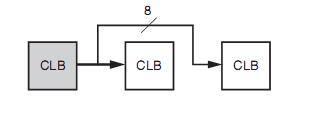

CLB:4 Slices;

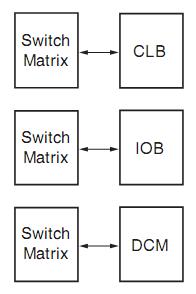

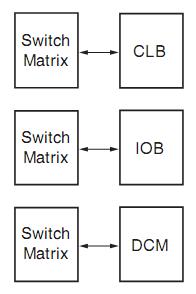

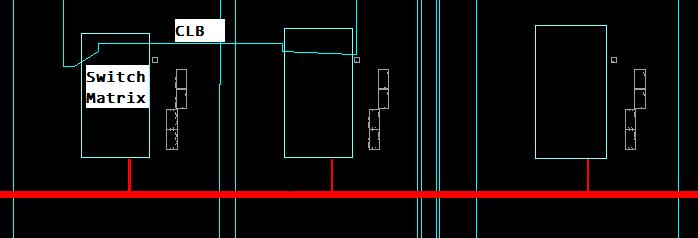

Tile:Switch Matrix + 功能单元(如CLB、IOB、DCM);下图所示:

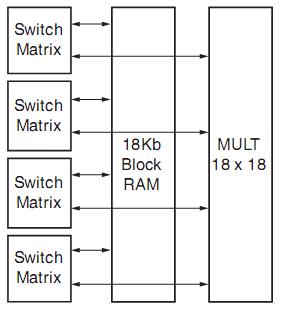

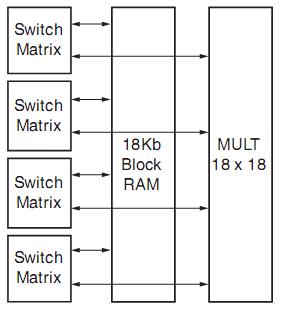

或者Multiple Switch Matrices + 功能单元(如BRAM、Multipliers);

下图为FPGA Editor的Tile图例

Tile上的布线资源有四种:Long Lines、Hex Lines、Double Lines、Direct Connections。

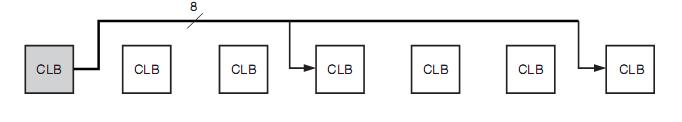

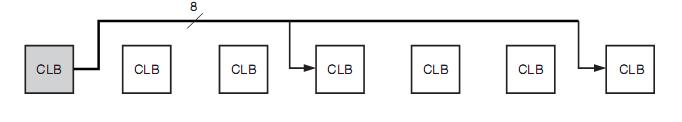

Long Lines:每条Long Line每隔5个Tiles链接一个Tile,每个Tile上有4条Long Lines,一行/纵Tiles共有24条Long Lines,且每行每纵都有;

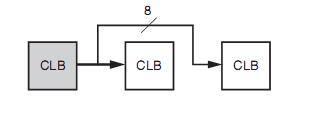

FPGA Editor图例:

Hex Lines:每条Hex Line每隔3个Tiles连接一个Tile,每个Tile上有32条Hex Lines(横向纵向各16条Hex Lines);(具体连接查看FPGA Editor)

Double Lines:每条Double Line连接横向或者纵线上相邻的两个Tiles,每个Tile上有32条Double Lines(横向纵向各16条Double Lines);

Direct Connections:每条Direct connect line连接八个方向上Tile;

Fullhex Line:该类型的布线资源在Spartan3的指导手册并没有涉及,但是从FPGA Editor可以清楚看到,每条Fullhex Line连接横向或者纵线上相邻的六个Tiles。

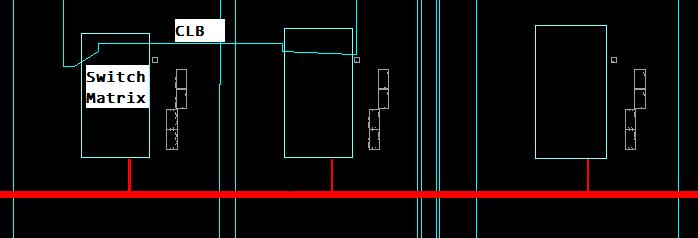

FPGA Editor图例如下:

上述各种线根据时序约束进行灵活的组合,达到时序收敛的目的。

补充(摘至网络,作者 王诚 钟信潮 吴蕾)第二全局时钟资源(对应上述的Long Lines)第二全局时钟资源也叫长线资源,它是分布在芯片的行、列的栅栏(Bank)上,一般采用铜、铝工艺,其长度和驱动能力仅次于全局时钟资源。与全局时钟相似,第二全局时钟资源直接同IOB、CLB、选择性块RAM等逻辑单元连接,第二全局时钟信号的驱动能力和时钟抖动延迟等指标仅次于全局时钟信号。Xilinx的FPGA中一般有比较丰富的第二全局时钟资源(很多器件有24个第二全局时钟资源),以满足高速、复杂时序逻辑设计的需要。

在设计中一般将频率较高,扇出数目较多的时钟、使能、高速路径信号指定为第二全局时钟信号。第二全局时钟资源的使用方法比较简单,一般是在约束编辑器的专用约束(Misc)选项卡中指定所选信号使用低抖动延迟资源“Low Skew”。也可以直接在指导Xilinx实现步骤的用户约束文件(UCF)中添加“USELOWSKEWLINES”约束命令。上面在约束编辑器中的操作等效于在用户约束文件中添加如下内容:

NET "sum<0>" USELOWSKEWLINES;

NET "sum<1>" USELOWSKEWLINES;

NET "sum<2>" USELOWSKEWLINES;

全局时钟资源是专用布线资源,它存在于全铜布线层上,用户使用全局时钟资源并不会影响芯片的其它布线资源。而第二全局时钟资源与之不同,它使用的是芯片内部的布线资源。在设计的密度非常大(面积利用率高于90%)的情况下,使用所有的第二全局时钟资源会给设计的布局布线带来负面影响,可能导致芯片布线不成功。

/2

/2

文章评论(0条评论)

登录后参与讨论