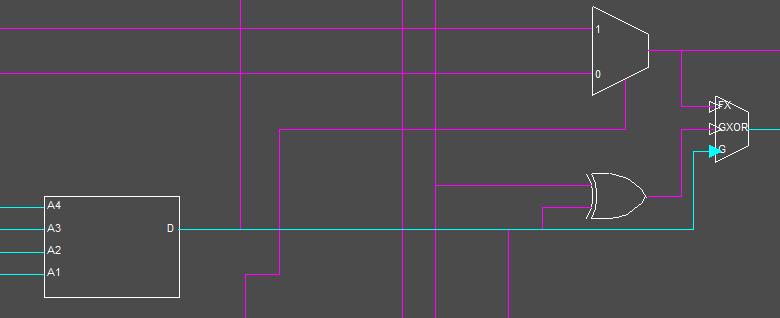

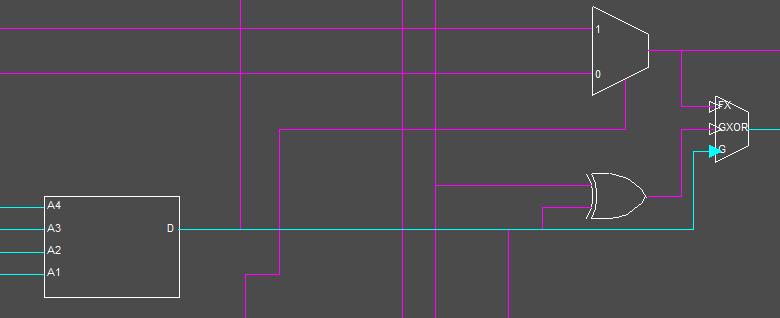

BEL Description

BEL is an advanced placement constraint. It locks a logical symbol to a particular BEL site in a slice. BEL differs from LOC in that LOC allows specification to the slice level. BEL allows specification as to which particular BEL site of the slice is to be used.

上述说明,BEL用于Slice内部的位置约束,而LOC仅限Slice以上的约束。

BEL Applicable Elements

。 Registers

。 FMAP

。 LUTs

。 SRL16s

。 XORCY

。 RAM (LUT)

。 RAM16XLS

可应用BEL约束的功能元件有Register、LUT等。

BEL Syntax

The UCF syntax is:

INST "instance_name" BEL={F | G |FFX | FFY | XORF | XORG};

where

。 F and G identify specific LUTs, SRL16s, distributed RAM components in the slice

。 FFX and FFY identify specific flip-flops, latches, etc. in a slice

。 XORF and XORG identify XORCY elements in a slice

下图是Slice内部G的说明:

而对应的Slice另一半就是F。

/1

/1

文章评论(0条评论)

登录后参与讨论