使用HDL Bencher生成激励(原创)<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

ISE使用HDL Bencher能自动生成测试文件(顶层文件)

1. 在Source工作区右单击New Source——Test Bench WaveForm

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

2. Next 选择要测试的文件,注意不要选择子模块

3.弹出Initial Timing and Clock Wizard

设置的参数有

Rising Edge:上升沿触发

Falling Edge:下降沿触发

Dual Edge:两个沿都触发

Clock High Time:时钟高电平保持时间

Clock Low Time:时钟低电平保持时间

Input Setup Time:输入建立时间

Output Valid Delay:输出有效时间

Offset:时钟偏移

input setup就是模拟的输入信号相对于时钟的建立时间,越大越有利于仿真,是固定的。(http://www.edacn.net/bbs/thread-14860-1-153.html )

设计类型分为3类:

Single Clock 单时钟同步时序电路,选择时钟信号clk

Multiple Clock多时钟同步时序电路

Combinatorial(or internal clock)组合电路

全局信号设置主要选择是否使用GSR(FPGA),PRLD(CPLD)等全局置位、复位信号

High for Initial:GSR或PRLD信号时间

(GSR,GTS 是芯片的全局复位和全局置位信号,使用不当反而会出问题,不必管它就是了)

Initial Length of Test Bench:设置仿真时长

Time Scale:设置仿真所用时间单位(ms,ns,ps)

Add Asynchronous Signal Support:需要进一步设置异步时序关系

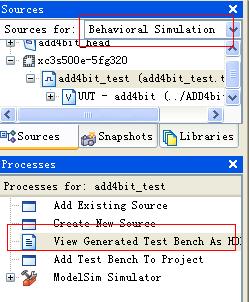

通过View Generated Test Bench As HDL可以看到设置参数的意义

……

parameter PERIOD = 200;

parameter real DUTY_CYCLE = 0.5;

parameter OFFSET = 100;

initial // Clock process for clk

begin

#OFFSET;

forever

begin

clk = 1'b0;

#(PERIOD-(PERIOD*DUTY_CYCLE)) clk = 1'b1;

#(PERIOD*DUTY_CYCLE);

end

end

……

PERIOD=时间高电平保持时间+时间低电平保持时间=周期

OFFSET=时钟偏移

DUTY_CYCLE=占空比=时间高电平保持时间、时间低电平保持时间

(PERIOD-(PERIOD*DUTY_CYCLE))= 时间低电平保持时间Clock Low Time

(PERIOD*DUTY_CYCLE)= 时钟高电平保持时间Clock High Time

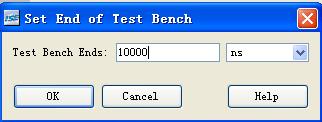

如果觉得仿真时间不够的话,可以右单击,选择set end of testbench。

设置仿真结束时间,得到下图:

也可以直接在跳出来的modelsim里直接run。

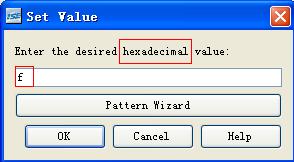

要给输入赋值时,在相应输入信号左单击,出来一个对话框

可以填入输入仿真的值,要注意所填值的格式,上面的是16进制,要改变进制的话,可以右单击:

好了,这样就可以给输入设置仿真值

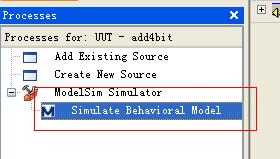

我用的是ISE 9.2i,好像没了测试激励的覆盖率分析,也不能用HDL Bencher仿真了,只能调用ModelSim仿真了L (没了Generate Expected Simulation Results选项)。

(http://www.dzkf.cn/html/EDAjishu/2008/0909/3346_3.html Xilinx使用入门 里面用的ISE是老版本)

如果是给组合逻辑编写仿真测试文件,可以这样:

1. New Source——Test Bench WaveForm——Combinatorial(or internal clock)

2. New Source——Verilog Test Fixture

【原创文章,转载请注明出处】

/7

/7

文章评论(0条评论)

登录后参与讨论