基于Verilog的VGA驱动设计(一)VGA时序分析<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

VGA时序分析

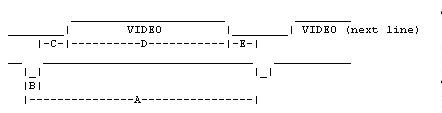

电阻DAC转换网络和640X480的VGA时序图:

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

图1

扫描频率

显示器采用光栅扫描方式,即轰击荧光屏的电子束在CRT屏幕上从左到右(受水平同步信号HSYNC控制)、从上到下(受垂直同步信号VSYNC控制)做有规律的移动。光栅扫描又分逐行扫描和隔行扫描。电子束采用光栅扫描方式,从屏幕左上角一点开始,向右逐点进行扫描,形成一条水平线;到达最右端后,又回到下一条水平线的左端,重复上面的过程;当电子束完成右下角一点的扫描后,形成一帧。此后,电子束又回到左上方起点,开始下一帧的扫描。这种方法也就是常说的逐行扫描显示。

Horizonal Timing

图2

A (us) Line PeriodB (us) Sync pulse lenght C (us) Back porchD (us) Active video timeE (us) Front porch

Vertical Timing图3

O (ms) Frame PeriodP (ms) Sync lengthQ (ms) Back porchR (ms) Active video timeS (ms) Front porch

Horizonal timing information 水平扫描时序

图4

Notes:

· Active area is actually an active area added with 6 overscan border pixels (in some other VGA timing tables those border pixels are included in back and front porch)

Vertical timing information 垂直扫描时序

图5

Notes:

· Active area is actually an active area added with 4 overscan border lines (in some other VGA timing tables those border lines are included in back and front porch)

· Note than when the active part of VGA page is widened, it passes by the rising edge of the vertical sync signal in some modes (marked with *)

根据上面的水平和垂直扫描时序可以分析显示800x600模式,FPGA系统时钟采用Spartan-3E Starter Kit板上的50MHz的有源晶振。为了显示器显示效果好,采用刷新频率为72Hz。

以下以系统时钟频率为50MHz,显示器显示800x600模式为例分析水平扫描和垂直扫描时序:系统时钟周期为1/50MHz=20ns

水平扫描Horizonal(Line)

A 水平(行)周期为1040个像素(Pix),时间为1040x20ns=20.8us;

B 同步脉冲为120像素(Pix);

C 后沿为61个像素(Pix);

D 有效时间为806个像素(Pix);

E 前沿为53个像素。

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

////////// 水平扫描参数的设定

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////parameter LinePeriod =12'd1040;

parameter H_SyncPulse=10'd120;

parameter H_BackPorch=10'd61;

parameter H_ActivePix=10'd806;

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

////////// 水平扫描计数

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

always @ (posedge clk or negedge rst_n)

if(!rst_n) x_cnt <= 1;

else if(x_cnt == LinePeriod) x_cnt <= 1;

else x_cnt <= x_cnt+ 1;

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

////////// 水平扫描信号hsync产生

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

always @ (posedge clk or negedge rst_n)

if(!rst_n) hsync_r <= 1'b1;

else if(x_cnt == 1) hsync_r <= 1'b0; //产生hsync信号

else if(x_cnt == H_SyncPulse) hsync_r <= 1'b1;

垂直扫描Vertical(Frame)

O 垂直扫描周期为666个行扫描,时间为666x1040x20ns=13853us;

P 同步脉冲为6个行扫描,时间为6x1040x20ns=125us;

Q 后沿为21个行扫描,时间为21x1040x20ns=436us;

R 有效时间为604个行扫描,时间为604x1040x20ns=12563us;

S 前沿为35个行扫描,时间为35x1040x20ns=728us。

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

////////// 垂直扫描参数的设定

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

parameter FramePeriod="10"'d666;

parameter V_SyncPulse=10'd6;

parameter V_BackPorch=10'd21;

parameter V_ActivePix=10'd604;

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

////////// 垂直扫描计数

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

always @ (posedge clk or negedge rst_n)

if(!rst_n) y_cnt <= 1;

else if(y_cnt == FramePeriod) y_cnt <= 1;

else if(x_cnt == LinePeriod) y_cnt <= y_cnt+1;

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

////////// 垂直扫描信号hsync产生

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

always @ (posedge clk or negedge rst_n)

if(!rst_n) vsync_r <= 1'b1;

else if(y_cnt == 1) vsync_r <= 1'b0; //产生vsync信号

else if(y_cnt == V_SyncPulse) vsync_r <= 1'b1;

并不是每个像素都能显示的,只有在有效区域像素区域内才能显示RGB

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

////////// 垂直扫描信号hsync产生

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

wire valid; //有效显示区标志

assign valid =

(x_cnt >= (H_SyncPulse+H_BackPorch)) &&

(x_cnt < (H_SyncPulse+H_BackPorch+H_ActivePix)) &&

(y_cnt >= (V_SyncPulse+V_BackPorch)) &&

(y_cnt < (V_SyncPulse+V_BackPorch+V_ActivePix));

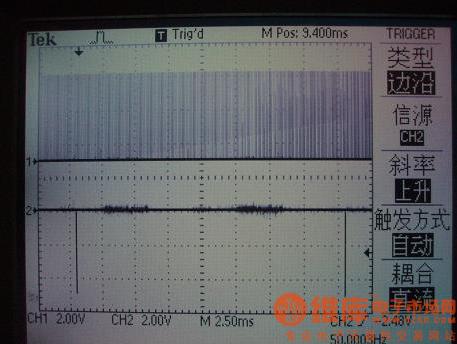

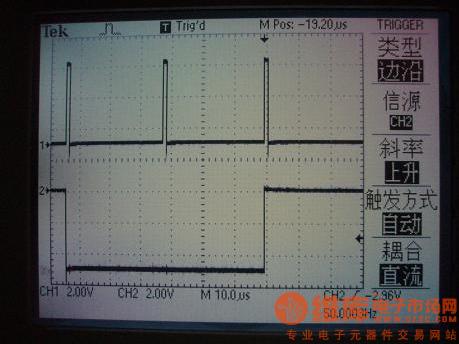

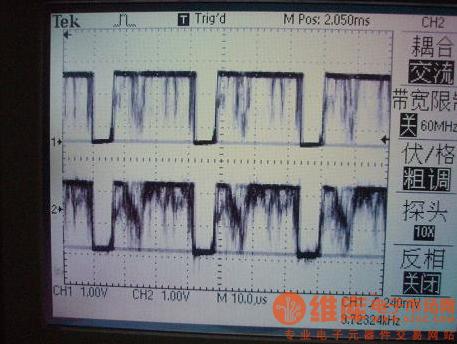

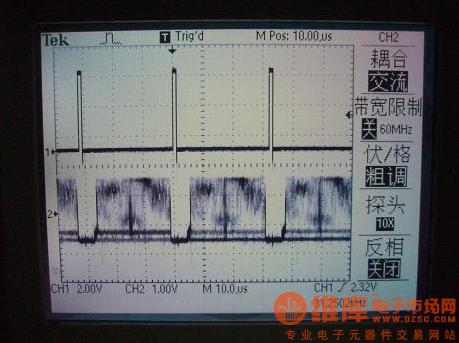

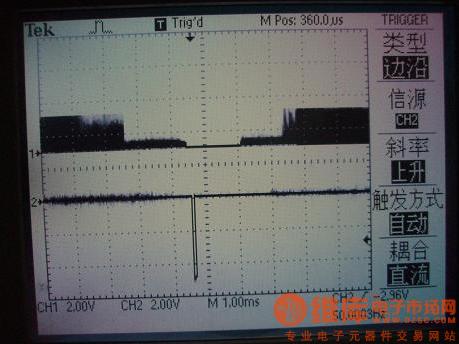

下面是测量逐行扫描60HZ的电视盒的VGA时序波形:

图6水平—垂直同步信号

图7水平—垂直同步信号

图8 RED-BLUE颜色信号

图9水平同步-R颜色

图10颜色R-垂直同步

图11

初步整理的时序

行周期32us(频率31.3Hz)

行同步脉冲时间7us

场频率60Hz

参考资料

1)VGA Signal Generation with the XS Board

2)CPLD驱动VGA显示器

http://blog.21ic.com/user1/636/archives/2007/43935.html

(图1)

3)VGA timing information

http://www.epanorama.net/documents/pc/vga_timing.html

(图2、图3、图4、图5)

4)瑞芯科技设计示例RHic013: 使用FPGA控制VGA显示

5)VGA Controller,Altium

http://www.dzsc.com/dzbbs/20070204/200765205519734395.html

(图6、图7、图8、图9、图10、图11)

/5

/5

用户377235 2014-8-9 21:45

请问你的那个水平同步信号是不是错了呢,不是负电平吗