————————————miaojf 发表于 2003-7-8 09:38

延时方面,CPLD可预测;FPGA不可预测;

★———————————westor 发表于 2003-7-9 13:18————积 分 1963 排 名 326

总的来说CPLD更多用组合逻辑做一些设计,FPGA则最好采用全同步时序逻辑设计。

————————————grey_yz 发表于 2003-7-9 20:38

但是有一点时确定的:CPLD的延时和布局没有太大的关系,而FPGA就不一样,她是和内部的布线和布局有关的,延时的大小和布线布局有关。

————————————老五 发表于 2003-6-20 10:03

从理论上来讲,maxplus2是不支持综合延时语句的,通常的方法都是用触发器来实现延时。而延时的分辨率由触发器的基础时钟决定。

★———————————东方不败 发表于 2003-6-20 10:10————积 分 6393 排 名 47

如果延时短的话用几个D触发器(几个时钟周期),长的话用计数器控制

————————————咖啡伴侣 发表于 2003-5-9 14:11

实际上,vhdl延时语句并不能在真正的硬件上产生任何作用。

————————————谭可 发表于 2003-5-9 16:15

是的,只是在仿真的时候才有用。要实现延时可在线路中加入lcell,不过altera不推荐。

————————————gaoke6151 发表于 2003-3-16 22:44

两个非门就可达到延时效果!否则就要加时钟

————————————LXJ_2587 发表于 2003-3-17 17:25

我感觉外接一个高频时钟之后有移位寄存器控制好一些

★———————————guilv 发表于 2003-3-21 11:03————积 分 1065 排 名 892

看看输入输出IO延时以及门延时是多少

————————————chiang 发表于 2003-3-24 17:32

50ns的延迟想单纯用组合逻辑和布线延迟实现,估计要浪费你n多宏单元。一般信号经过一级宏单元的延迟也就1、2个ns(具体要查DATASHEET),你自己算要多少宏单元吧。

所以还是用时钟计数的可靠。

另外就算时钟计数,也存在问题,输出的B信号与内部时钟同步,无法保证和A信号的时差在50ns这个值上。50ms就好做得多了,毕竟百分误差小得多。

另一个角度,在片外用个RC滤波加个丝米特触发器之类的东东是不是可以实现呢,配好了也许可以

————————————EricGuo 发表于 2003-3-12 17:59

请教如何在ISE中将一个信号延时一点(几个纳秒,小于系统时钟周期),在 MUXPLUX2中好象可以加硬BUFFER,保证在综合中不被优化掉,请问在ISE 中如何处理?

————————————yigong 发表于 2002-12-8 17:14

可以用cell来实现延迟!

————————————JACK DENG 发表于 2002-12-5 14:52

建议用高频时钟计数

用buffer延时,无法准确控制延时时间,并且任何元件上升沿和下降沿的延时都不一样,没法算的。

★———————————amberyn 发表于 2002-12-5 15:22————积 分 1185 排 名 749

小延时用buffer大延时用时钟控制

但是不会很精确,不知道谁有好办法

★———————————xrjy 发表于 2002-12-5 18:50————积 分 2142 排 名 281

肯定要时钟来产生,

门延时是不可预算的,且每次综合都会有偏差,after等延时语句是不可综合的

————————————jovil 发表于 2002-12-5 19:39

如果要延时可控,就要用时钟,

————————————JACK DENG 发表于 2002-12-6 15:41

要精确实现延时 只能说明设计思路有问题

————————————johnthan 发表于 2002-10-31 16:39

如果是altera公司的器件很短的延时都可以控制,但是并不是软件中仿真给出的值,因为信号在内部两个lab之间的延时与信号在单个lab中不同cell块之间的延时不同,后者快的多。在软件中可以设定功能块做在一起或是分散开以获得不同的小的延时。

————————————zeb 发表于 2002-7-24 20:16

可以通过计时器触发的方式得到延迟

————————————hunter425 发表于 2002-3-10 19:15

是的,用语言编写的延时功能实现不了,只能用原理图实现

————————————hunter425 发表于 2002-4-19 20:22

可以延时

在原理图中调用LATCH模块可以实现严格意义的5nS延时,更长的延时可以用计数器实现

————————————superwxj 发表于 2002-4-12 22:54

原理图怎么做延时???!用反相器吗?那样会被优化掉?请赐教!

————————————bigtigerlu 发表于 2002-4-14 08:31

可以有几种方法,

1.用倍频器直接输入所需时钟,印制板布线要很讲究;

2.使用可以倍频的片子,这种片子对软件要求较高;

3.采用双50MHz时种,处理逻辑较为复杂,但对电路要求与芯片要求都低了.

我用过1、3种方法,第2种没试过,你如果有能力可用2方法,实现简单但成本可能要高些.

————————————reticle 发表于 2002-3-20 10:16

1,因为你用的是fpga,所以可以在布局布线完成后,自己手工改一下版图,满足延时的要求。

2,不加非门,用2输入的与门,把另一个输入接到pad上,这样就不会优化掉,然后在外围电路中巴pad接到地上。

★———————————vhdl 发表于 2002-1-22 15:04————积 分 19811 排 名 6

lcell

不是好办法

★———————————jzt369 发表于 2002-1-24 09:43————积 分 1189 排 名 742

可以用lcell延时,但是会产生另外一个问题。

这

样产生的延时随环境变化而变化(如温度),你的延时就变得不稳定,你要了解CPLD的内部结构,这个延时就是宏单元的输出到输入的延时(这只是笼统的理

解),延时主要和器件的速度相关,如你所说的10ns,这就是器件的速度等级。要比10ns更小可能不好办,本身器件的原因,这个延时只是个极限指标,其

实每个宏单元的延时的一致性并不是很好。建议不要采用这种延时,能不用就不用。

★———————————kinggx 发表于 2001-11-30 09:12————积 分 3729 排 名 118

fpga的延时问题据说很讨厌

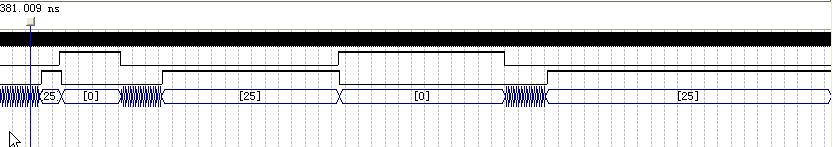

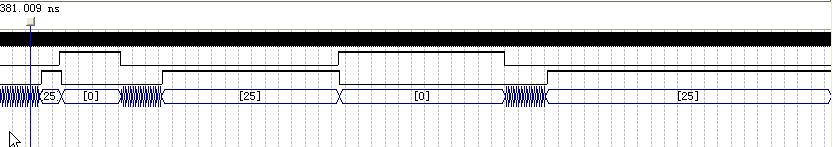

下面是我自己的一个例子:

要求: 输入时钟50m:

输出的信号是输入信号的反相,但是输出信号在输入信号变为低电平以后延时需要延时一段时间再变为输入信号的反相

我使用计数器来达到延时的要求,代码:

module clk_tra_delay(clk,sig_in,sig_out);

input clk;

input sig_in;

output sig_out;

reg sig_out;

reg [4:0]deley_cnt ;

always @ (posedge clk)

begin

if(sig_in)

begin

deley_cnt <= 5'b00000;

sig_out <= ~ sig_in;

end

else if(deley_cnt == 25)

begin

deley_cnt <= 25;

sig_out <= ~sig_in;

end

else

begin

deley_cnt <= deley_cnt + 5'b00001 ;

sig_out <= sig_in;

end

end

endmodule

仿真结果:

这样我就可以保证 我输出的数据在信号的上升沿输出的时候 输出的是更新过的数据

/5

/5

zhangshaobing517_935512703 2009-5-19 18:43

用户1442376 2009-5-19 18:08