如果汽车电子模块有不用的引脚,那么我们如何去处理呢?

我们在处理时,可以考虑直接连接到地平面上去。(参考福特公司的处理方案ELCOMP17)

(Modules that have spare pins (never used in any version using the same PCB); these pins shall be tied to the module ground plane.)

如果有射频接受模块的话,这些引脚的接地可能会造成射频接受性能的降低,这时候就不能使用接地的方式了,必须使用ESD的电容和放电电阻来消除静电的影响了。

还有一种例外也是很常见的,如果这些不用的引脚附近有电源或者HSD输出的时候,我们就必须考虑把这些引脚接电容或者地了。显而易见的是,如果这些引脚相邻小于5mm,在不断的插拔过程中,引脚可能弯曲,这样会引起严重的断路事故,这是不被允许的。

当然ESD电容和放电电阻不一定必须接到地,也可以接到阻抗低的电源。以上所有的措施都是为了防止静电从意想不到的路径传递到板上。

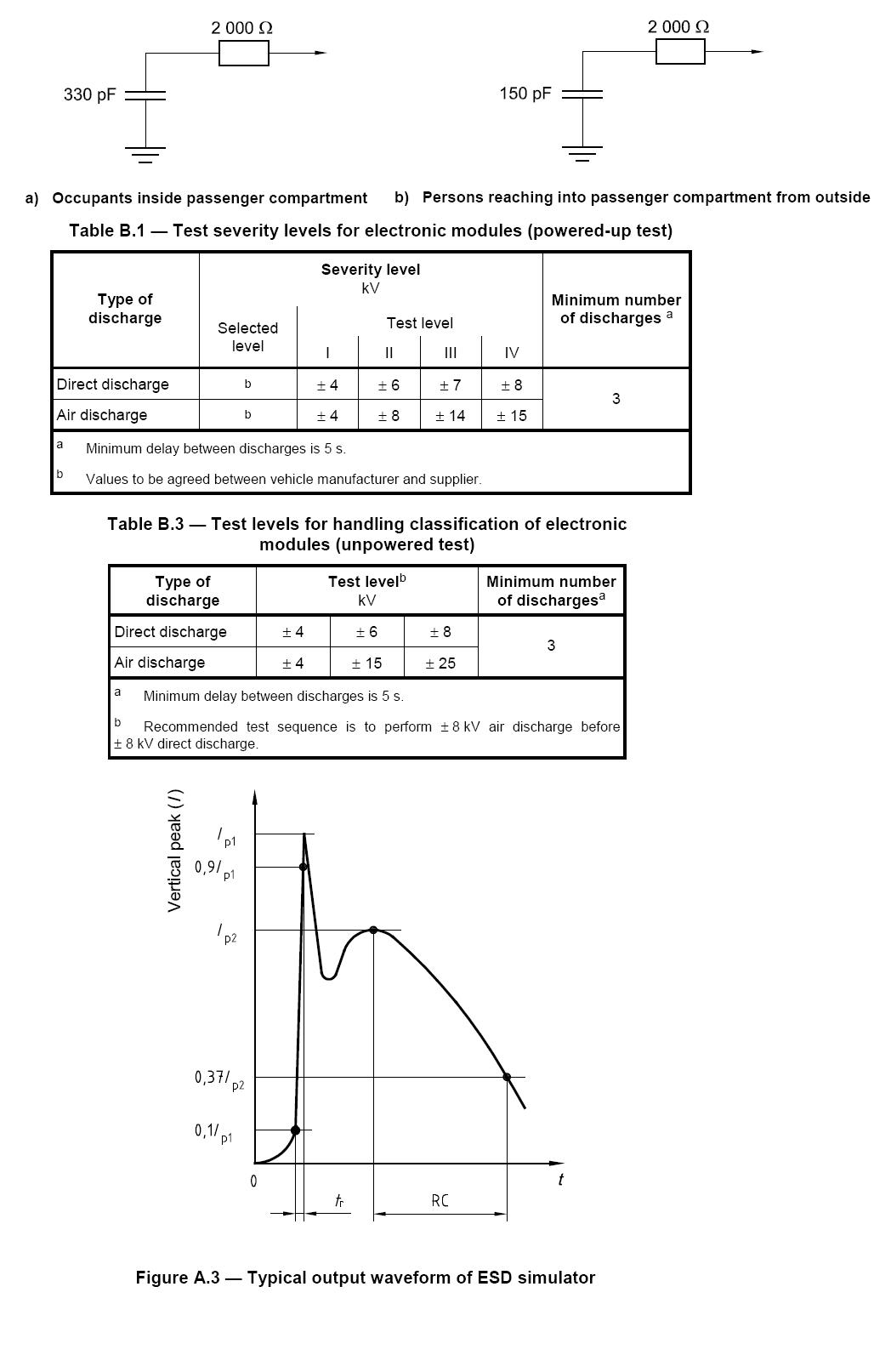

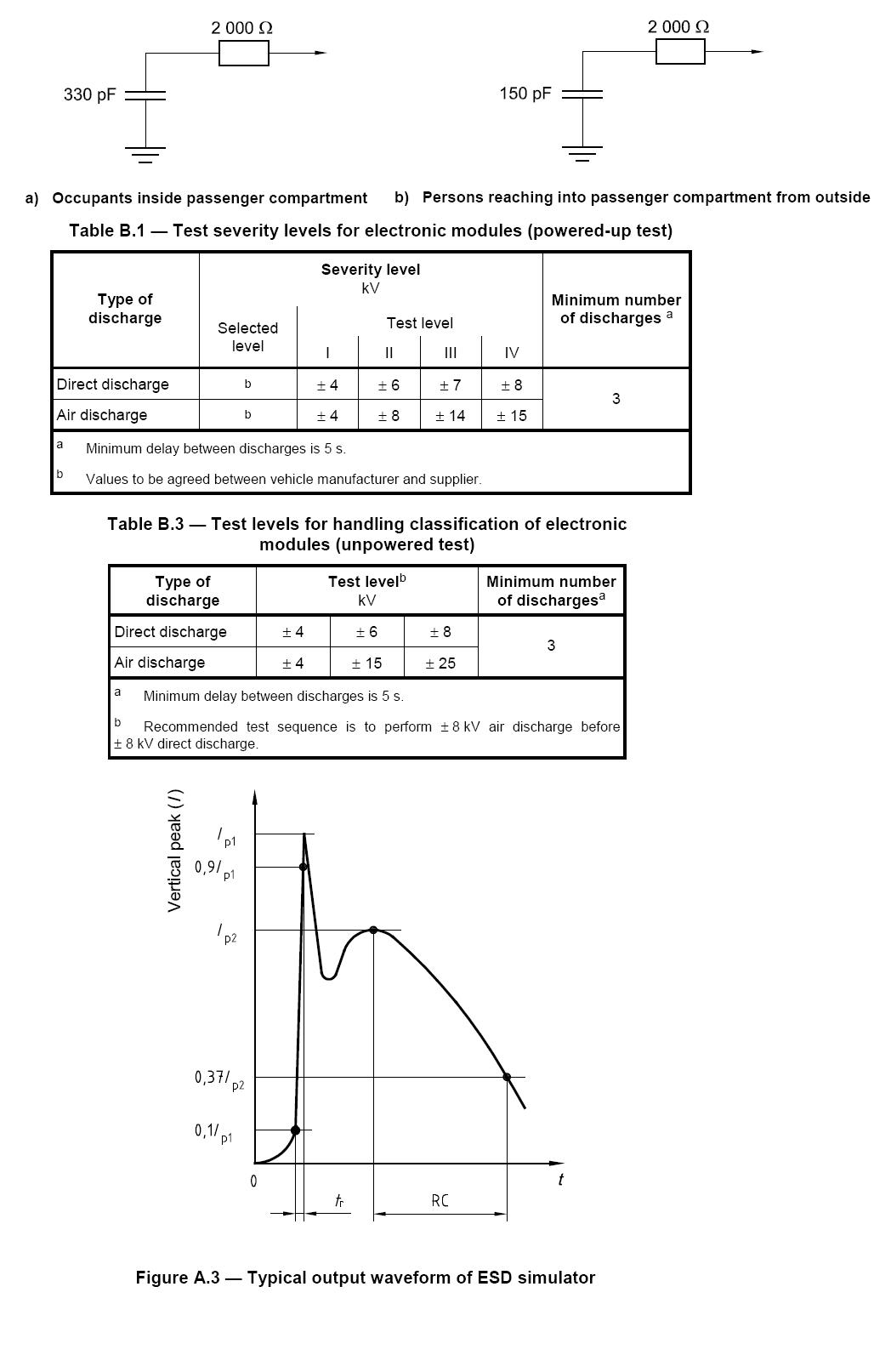

我们看看ISO10605的描述

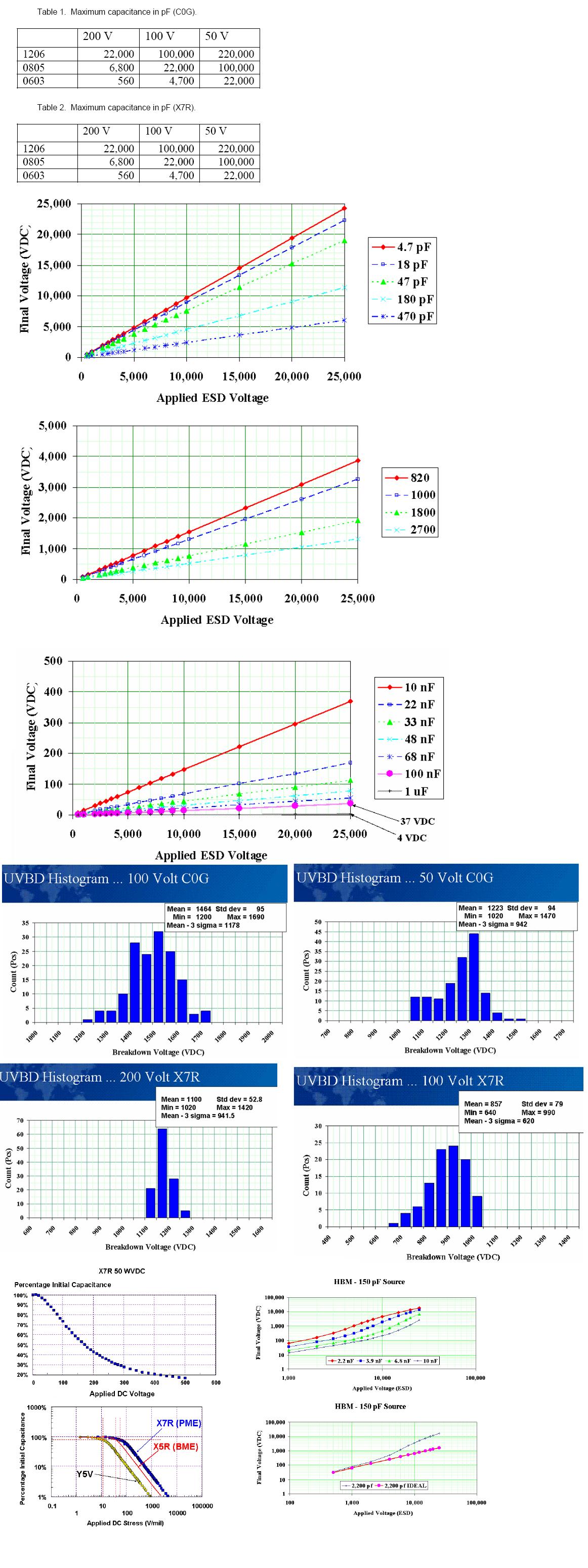

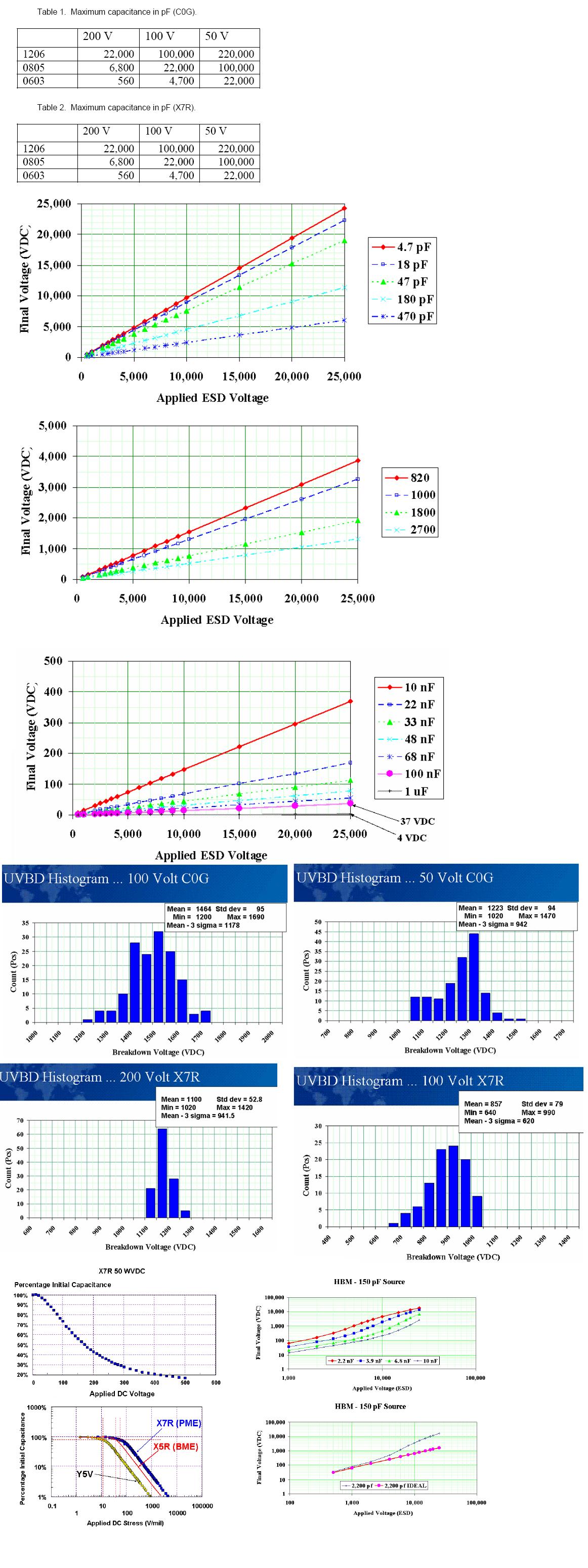

我们在设计ESD电容的时候,电容的容值是有限的,额定电压也是有限地,该如何去选取呢?总结如下:

Applied Voltage Levels

- For a specific ESD test Level, the lower the value of capacitance under test, the greater the voltage applied.

- Higher values of capacitance can withstand high levels of ESD pulses。

- The actual applied voltage is also limited by air discharge, which is a function of the case size.

- Capacitor Capabilites

ESD电压大小和电容容值

对于特定ESD测试,容值越小,加到电容上的电压越高,参考ESR放电模型可以得出这样的结论。

电容容值大,可以抵抗较高的电平。实际加在电容上的电压受空气放电的影响,和外壳容器大小是相关的。

Dielectric materials and Rated Voltage

- C0G will wishstand higher levels of ESD for the same voltage rating and capacitance value

- Higher voltage ratings are important if higher ESD levels were going to be involved

- For the same chip size, as the voltage rating increases, the maximum capacitance available decreases

填充材料和额定电压

这里有几点要注意的,首先C0G这种材质的电容最稳定也是性能最好的对于过ESD实验来说,其次电容的额定电压越大过高等级的ESD实验越有帮助。最后同样尺寸的电容,额定电压增加时,容值是受限的(电容发展越来越快的情况下,这种情况在改善。)

Chip Size

- Chip size has little effect on basic ESD capability,providing the same capacitance value is available at the same voltage rating

- For smaller chip sizes, the maximumu availabe capacitance at the same voltage rating decreases

- Reduction of chip size should be evaluated carefully for ESD critical appliactions.This is especially true if it is necessary to trade off voltage rating or capacitance value

- Use of 0603 chip sizes will most likely result in lower ESD levels.Air Breakdown is a factor to be considered

- Chip sizes samller than 0603 should not be used in ESD critical Applications

电容封装大小

电容大小对ESD能力影响不大,如果是同样的容值和同样的额定电压的情况下。

越小的封装,其最大可实现的容值是受限制的,在额定电压情况相同的条件下。

减小电容封装在严酷的ESD要求下需要谨慎。

0603的电阻普遍用在低ESD要求下,空气击穿是一个主要因素。小于0603不能使用。

Voltage Coefficient

- C0G dielectric materials are close to ideal, and are not affected by voltage coefficients

- X7R dielectric materials are Ferro electric, this effect increase the voltage applied

- Higher voltage ratings are again desirable to reduce the impact of the voltage coefficient on the voltage applied

- Smaller size chips may also influence the impact of the voltage coefficient

电压增加对容值的影响,C0G来说几乎不变,X7R会增大,额定电压高会削弱这种影响。小封装也会对此起作用。

下面为实验和分析数据,摘自KEMET分析报告

/4

/4

用户1404883 2010-5-20 01:40

用户1522876 2010-5-18 11:51