| 作者: 时间:2008-12-09 来源: | |

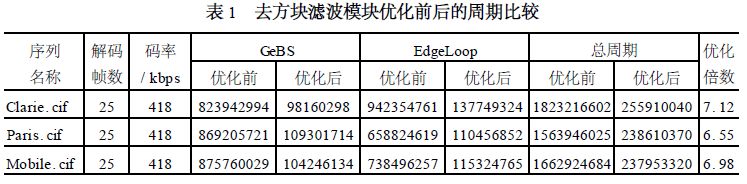

| 引 言 随着多媒体技术的快速发展,DSP 在各种电子消费 品中的地位日益突出。多媒体应用正在逐步走向网络化、 多样化、智能化。其中,ADSP 处理器在嵌入式网络多媒 体应用中有着显著的优点:性价比高,体积小,功耗低,外 围接口电路设计简单。目前广泛应用的处理器之一是 ADSP BF533 ,它适合于数码相机、便携式多媒体播放 机、网络媒体适配器、数据和多媒体网关、互联网协议( IP) 机顶盒、2. 5G和3G 无线手机以及汽车信息娱乐与安全 系统等各种应用。ADSP BF533 处理器使用方便,具有 良好的代码兼容性以及极高的性能和极低的功耗。本文 在介绍ADSP BF533 特点的同时,对其在设计应用中的 注意事项及优化方法做了相应的论述。在设计过程中,多 注意细节和优化方法可使设计更加顺利的实现,并为大规 模算法的执行提供有效的时间。 1 ADSP BF533 处理器简介 ADSP BF533 是ADI 公司推出的嵌入式多媒体处 理器,拥有运算频率高达750 MHz 的DSP 内核;采用ADI 公司与Intel 公司共同开发的MSA 体系结构[ 1 ] (微信号结 构) ,这种结构采用了一个综合的信号处理和控制指令集。 这样处理器就不仅是带有增强指令集的DSP ,也不仅是带 有2 个算术逻辑单元的MCU ,而是为同时运行控制指令 和算术指令而进行优化的处理器结构[ 2 ] ,集DSP 和MCU 功能于一身,从而消除了传统的多个不同处理器之间联系 的复杂性。 从讨论C 语言优化的角度出发,ADSP BF533 处理 器具有以下特点: ①处理器支持与分级存储结构相结合的改进型哈佛 结构,最高时钟频率为600 MHz , 峰值处理能力为1. 2 GMIPS。通过对工作频率及电压的动态调节可实现极低 的功耗。动态电源管理完全是由软件实时控制的,可以在 运行时随时改变内核电源,以降低功耗,效果非常明显。 ②ADSP BF533 DSP 内核包括2 个40 位的算术逻 辑单元(ALU) 、2 个乘法器累加器(MAC) 、4 个视频ALU 和1 个移位器。ADSP BF533 的硬件结构具有很高的并 行性和运算能力,可以进行双16 位数的加减、交叉和移位 运算,在设计中可以提高运算速度,并使复数运算大大 简化。 ③处理器的指令集[ 3 ] 包含了大量的运算指令,可以 快速执行固定点和小数运算,如乘加器和MAC shift 指 令等。 ④处理器可以实现零开销硬件循环,其效率比通过 条件分支返回循环起点的方式高得多。 ⑤处理器将成组的寄存器与函数单元相关联,从而 加快了运行速度、降低了功耗。例如,Blackfin 处理器既 有运算寄存器或d2reg 寄存器,又有地址寄存器或preg 寄 存器。 ⑥DMA[4 ] 数据的重排功能可以优化图像数据在内 存中的存储,这不仅可以提高内部存储空间的利用效率, 也可以提高数据的传输效率。虽然图像数据的传输也可 由软件实现,但会消耗大量的CPU 时钟周期,从而使DSP 的高速性能难以发挥,而由DMA 来完成同样的工作却不 占用CPU 的时钟周期。 2 硬件设计时的注意事项 采用ADSP BF533 处理器设计产品时,为了避免一 般的错误,除了要熟悉相关的规格书、硬件参考手册[5 ] 以 及处理器的勘误表外,在元器件的选择、中断和复位的设 置以及信号的完整性方面也要特别地关注。如果考虑周 全,设计仔细,那么整个系统的设计将减少大量的重复工 作,从而缩短设计周期。 (1) NMI 极性 NMI 全称为Non Maskable Interrupt ,即非屏蔽中断 请求信号。对于ADSP BF531/ 532/ 533/ 535/ 561 ,NMI 引脚激活为高电平;对于其他的处理器,NMI 引脚激活为 低电平。只有这样,才便于同标准的外围设备连接。同 时,也要注意NMI 引脚是否可用它的非激活状态,特别是 不能让NMI 引脚悬空。 (2) 电压范围 直接将5 V 电压连接到引脚可能会损坏引脚,并产生 故障。当Blackfin 处理器输出连接到5 V 输入设备时,可 能会引起引脚左漂移或被上拉到5 V ,而大多数处理器引 脚(除了两线接口引脚) 是不能超过5 V 电压的。所以,引 脚的电压变化应当保证在其规定的电压值或小于其许可 范围的最大值内,高电压中采用限流电阻是不能起到完全 的保护作用的。 (3) 信号完整性 破坏信号完整性将直接导致信号失真、定时错误,以 及产生不正确的数据、地址和控制信号,从而导致系统延 误甚至崩溃。快速的信号上升时间和下降时间是引起信 号完整性的主要问题。处理器的每个引脚上升、下降斜率 不同,一些引脚对噪声和其他引脚的信号反射具有很大的 敏感性差异。采用简单的信号完整性处理方法可以防止 线上传播反射信号干扰时钟和同步信号,其中短的走线和 阻抗特性对以下的信号显得尤为重要: ①CLIN K引脚应当有相应的驱动阻抗匹配; ②SPORT 口信号( TCL K,BCL K,RFS , TFS) 应当采 用终结; ③ PPI 引脚(如PPI2CL K和同步信号) 也同样受益于 标准的信号完整性技术。 (4) 复 位 Blackfin 处理器的引脚没有滞后作用,因此需要一个 单调的上升或下降过程。同时,复位引脚不能直接连接到 R/ C 延时电路上,因为Blackfin 处理器对这种电路噪声比 较敏感,所以在设计复位电路时应当由一个复位芯片产生 一个复位信号。 (5) 旁路电容 当高速的电路对内部供电端加上适当的旁路电容时, 对于电容的选择有两件事需要特别考虑: ①当处理器运行频率高于100 MHz 时,电容要小, 而且走线应当短以减小感应系数。如果选择0402 的表贴 电容,会比更大尺寸的电容效果要明显。 ②小电容值比大电容值更容易引起LC 电路的自激。 在低于50 MHz 时应采用几个0. 1μF 的电容;在高于500 MHz 时则应采用VDD2INT 旁加0. 1 p F、0. 01 p F、0. 001 p F 和100 p F 的组合电容。 3 C 语言的优化方法 在对C 程序进行性能优化时,主要包括编译器的自 动优化和编译器无能为力的人为算法优化。在一般情况 下,算法优化总是比编译器优化更为有效。因此,在设计 时应当首先进行算法优化,检测评估当前的算法是否适合 在Blackfin 处理器上运行。在评估C 程序时,应检查其一 般运行情况以及“别名判别”特性,判断编译器是否能够始 终理解正在调用的数据。 同时,在对C 程序进行优化时,还必须结合所用处理 器的处理能力。在处理能力方面,不同的目标处理器各有 所长,各自具有针对某种数学运算特性而专门编写的指 令,如维特比(Viteribi) 运算、位多路复用、向量乘法和加 法等。在设计时这些都必须考虑,采用自己选择的算法, 以确定处理器是否能够实现这些运算。 最后,还要考虑不可移植部分的更改。之前讨论的优 化都是维持一个可以在任何平台上运行的C 程序。如果 在程序中添加某些针对Blackfin 处理器的代码,那么更改 后的程序将不可导入其他处理器;否则,要重新编写部分的 C 代码、添加编译指示,或在代码行中添加汇编语句。为了 修改方便,可以保留一个C 模型备份,以便进行验证。 3. 1 编译器优化 编译器是当今软件开发中最基本的工具。编译器的 性能[ 6 ] 将直接影响生成的可执行程序的性能。其中,改善 程序性能的最快捷、最简单的方法是使用具有优化功能的 编译器。一个好的编译器可以充分利用处理器的特性,使 优化工作自动化,而不必去翻阅厚厚的处理器手册。 编译器的优化设置是在Visual DSP + + 4. 5 开发环境 界面的“编译(compile) ”对话框中进行,也就是通过菜单 “项目(project) ”→“项目选项(project option) ”,对该对话 框进行设置。 在进行编译器自动优化设置时,可以对“输出列表文 件”、“保存临时文件”、“产生调试信息”、“跳过预处理”等 优化项进行适当的选择,使编译器的性能达到设计时的 要求。 3. 2 源码优化 算法优化是程序设计的关键,为了提高程序代码[7 ] 的 效率,必须对要处理的源码进行一定的优化。源码大部分 是用C 语言写成,所做的优化工作包括: ①使用寄存器变量代替局部变量。 ②尽量避免使用超过三重循环的运算,因为ADSP BF533 拥有2 个硬件循环寄存器。充分利用这两个寄存 器,可以实现零开销的硬件循环。 ③在编写循环时,应使得上一次循环与下一次循环 没有相关性,并使用“# pragma VECTOR2FOR”标记内层 循环。通知编译器生成向量指令,硬件可以并行执行2 次 循环。 ④尽量用定点运算。由于ADSP BF533 没有硬件 浮点单元,所以用定点运算比浮点运算要快得多。 ⑤对于sin() 和cos ( ) 这样的复杂函数,可将常数数 组存储于内部全速SRAM 中,用查表来代替。调用AN2 SIC 的sin () 函数需要上百个周期,而用查表方法只需2 个周期。 3. 3 具体优化过程 优化是有侧重点的,优化是一门平衡的艺术,它往 往要以牺牲程序的可读性或 者增加代码长度为代价。虽 然有时可以通过优化程序代 码来提高程序的运行速度, 但在更多的时候, 需要针对 采用的特定硬件, 对程序进 行专用化来提高其运行速 度。最终, 将会构建一个速 度更快,但也更大、更复杂,并且不适于导入其他处理 器的专用程序。 下面分3 个层面来重点讨论如何进行优化: ①首先是程序优化,即尽可能利用编译器的自动优 化特性,实现代码优化。对于信号处理循环,编译器优化 相当有效,可以实现近20 倍的速度提升。但是,必须注意 的是,编译器优化只对部分代码区域有效。编译器优化不 能改变程序的算法,不会对程序进行全局更改,也不能大 规模重新排列数据。就编译器而言,正确性始终比提高性 能更重要。我们的目的就是为编译器提供一个安全的环 境,让其放心大胆地生成运行速度更快的代码;否则,它将 采取保守策略。 ②第2 步就是修改程序。只有在不得已的情况下, 才对程序进行必要的修改。要将导入处理器的现成的C 程序精心构建成所谓的“优化C 程序”,可以在其中添加 一些编译指示,其他编译器会将这些编译指示当作代码注 释,从而维持一定程度的可移植性;还可以在一定范围内, 对内置函数和存储限定符等代码进行同样的修改。 ③最后可以有针对性地重新编写部分代码,针对采 用的Blackfin 处理器的特性,利用专门特定的程序指令进 行修改程序,以提高效率。 为了最大限度地缩短设计周期和产品的上市时间,可 以采用以下的优化模型:首先,确定性能目标;然后,将C 程序导入Blackfin 处理器;再依次执行上述优化步骤,最 后逐渐实现预设的性能目标。 4 优化实例 下面以去方块滤波模块为例,简要说明代码优化前后 的差别。测试优化效果的方法:将参考代码JM8. 6 中的 去方块滤波C 程序模块[8 ] 加到原有的解码器中进行测试, 再与经过优化的程序模块的测试周期进行对比。选择的 测试图像序列为Clarie. cif 、Paris. cif 、Mobile. cif ,测试数 据如表1 所列。  从表1 可以看出,与优化前的JM8. 6 中的C 程序代 码相比,经过优化后的去方块滤波汇编模块效率提高了7 倍左右。 结 语 本文针对多媒体处理芯片ADSP BF533 的结构特 点,重点阐述了在设计过程中的注意事项和程序优化方 法。随着Blackfin 处理器的普及,ADSP BF533 已经广 泛应用于各种电子工程,相信本文对ADSP BF533 的学 习和应用开发能起到一定的帮助作用. |

| 标签: DSP ADI 3G 互联网协议 ADSP BF533 |

/2

/2

用户1539068 2009-12-8 20:21

用户188034 2009-9-14 19:35