| 作者: 时间:2008-12-09 来源: | |

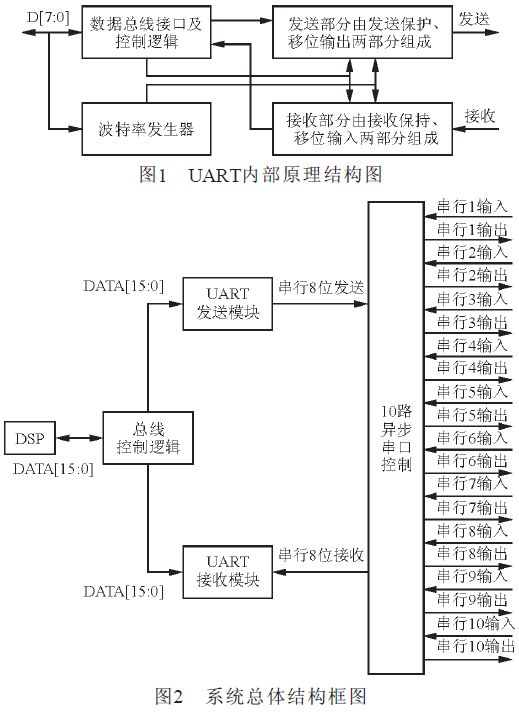

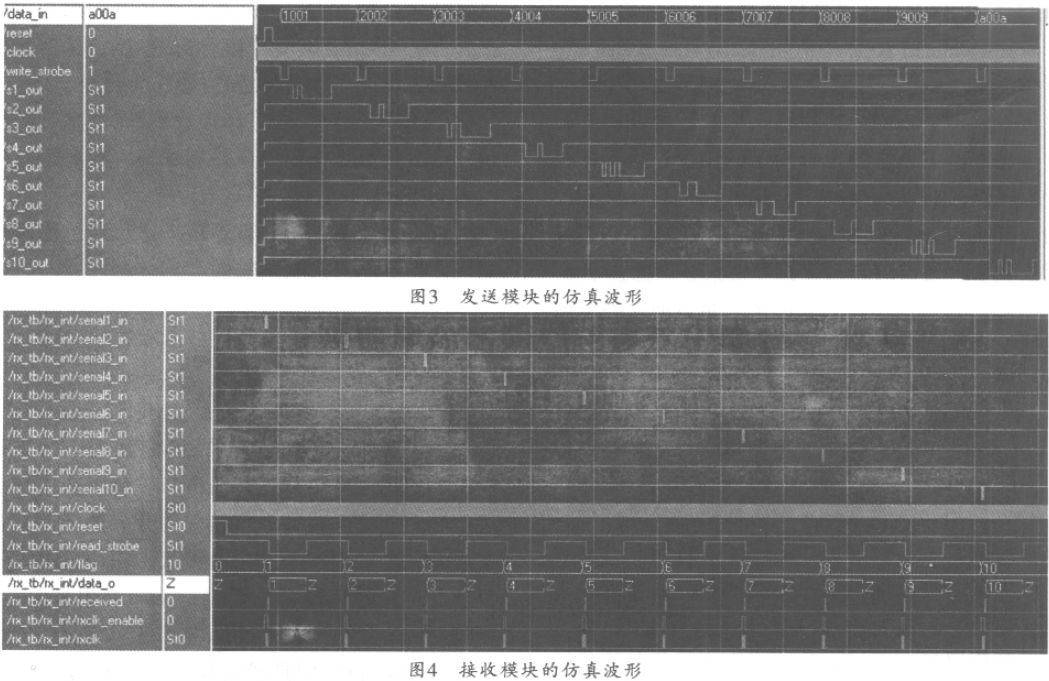

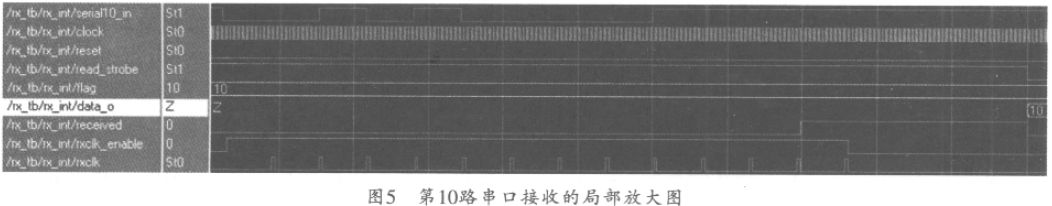

| 摘要: 在介绍了ADSP- BF533处理器的基础上, 给出了基于ADSP- BF533和CPLD设计具有 多路UART接口的系统设计方法, 该方法克服了一个系统中的ADSP- BF533不能满足多个 UART接口的缺点。文章最后还给出了基于ModelSim的仿真波形。 关键词: 异步串口; 分频; ModelSim; 多路UART接口 0 引言 目前, 在数字信号处理技术中, DSP+CPLD 是控制接口设计中比较常用的方式。然而, ADSP- BF533虽有异步串口, 但该芯片只有一个异步 串口, 当一个系统中出现多个UART接口时, ADSP- BF533就显得无能为力了。为此, 本文采 用CPLD来实现多路UART接口的设计, 以满足 ADSP- BF533与多路UART接口的通信。 1 ADSP- BF533简介 ADSP- BF533处理器是Blackfin系列产品中的 一员。其最大工作频率可达600 MHz。Blackfin处 理器内核包含有2个16位乘法器、2个40位累加 器、2个40位ALU、4个视频ALU 和1个40位移位 器, 可处理来自寄存器组的8位、16位或32位数 据。 该处理器包含有丰富的外设, 可通过不同的 高速宽带总线与内核相连。该系统不但配置灵 活, 而且有极好的性能。通用外设包括UART、 带有PWM (脉冲宽度调制) 和脉冲测量能力的定 时器、通用I/O标志引脚、实时时钟和看门狗定 时器等。 该处理器有多个独立的DMA 控制器, 能够 以最小的处理器内核开销自动完成数据传输。 DMA传输可以发生在ADSP- BF533处理器的内部 存储器和任一有DMA 能力的外设之间。此外, DMA 传输也可以在任一有DMA 能力的外设和已 连接到外部存储器接口的外部设备之间完成(包 括SDRAM控制器、异步存储器控制器)。有DMA 传输能力的外设包括SPORTs、SPI 端口、UART 和PPI 端口。每个独立的、有DMA 能力的外设至 少应有一个专用DMA 通道。 ADSP- BF533处理器有16个双向通用可编程I/ O引脚(PF15- 0)。每一个可编程引脚对标志控制 寄存器、标志状态寄存器和标志中断寄存器的编 程均可独立控制。标志方向控制寄存器可规定每 个独立的PFx引脚的方向, 并可用作输入或输出。 ADSP- BF533该处理器提供有1个全双工的通 用异步接收/发送(UART) 端口, 并与PC标准的 UART完全兼容。UART端口可为其它外设或主机 提供一个简化的UART 接口, 并可支持全双工、 有DMA 能力的异步串行数据传输。UART端口可 支持5~8个数据位、1或2个停止位以及无校验、 奇校验、偶校验位。UART端口的波特率、串行 数据格式、错误代码的产生和状态、中断等均可 编程设置。 2 ModelSim仿真工具 ModelSim为HDL仿真工具, 利用该软件可对 所设计的VHDL或Verilog程序进行仿真。Model-Sim 支持IEEE常见的各种硬件描述语言标准。 Modelsim仿真工具是Model公司开发的。它 可以支持Verilog、VHDL以及它们的混合仿真, 也可以将整个程序分步执行, 使设计者直接看到 自己程序的下一步要执行的语句, 而且在程序执 行的任何步骤、任何时刻, 都可以查看任意变量 的当前值, 也可以在Dataflow窗口查看某一单元 或模块输入输出的连续变化等情况, 因而比quartus 自带的仿真器功能强大的多, 是目前业界最通 用的仿真器之一。 3 异步串口原理 UART(Universal Asynchronous Receiver/Transmitter) 通用异步收发器是用于控制计算机与串行 设备的芯片。它提供有RS- 232C数据终端设备接 口, 因此, 可以通过计算机和调制解调器或其它 使用RS- 232C接口的串行设备进行通信。UART 内部结构原理如图1所示。图2所示是其系统总体 结构框图。图2中的总线控制逻辑主要用于完成 数据总线的方向控制。 UART发送模块中16位并行数据的高4位用来 控制是发向第几路的数据, 低八位则是要发给该 路异步串口的数据。发送模块中还有一部分用来 把并行低8位数据转化成串行8位数据, 然后再根 据并行数据的高4位判断发往哪一个异步串口。 UART接收模块中, 把接收到的8位串行数据 转化成并行数据送到总线控制逻辑, 然后通过中 断通知DSP来读取。 这样就实现了通过DSP的并行数据总线来控 制10路异步串口的收发数据。  4.2 接收模块的仿真波形 在EPM7128中编程检测输入串口数据的下降 沿, 并使能接收时钟, 然后即可开始接收数据。 接收数据时, 要把接到的第一位数据去掉, 然后 取第2~9位数据, 这样就把起始位去掉了, 从而 得到八位数据。接收模块的仿真波形如图4所示。 serial1_in~serial10_in是第一路到第十路串口 的接收端口, 它们的输入数据依次是1~10; clock 是系统时钟; reset 是系统复位, 高电平有效; read_strobe是DSP的读信号; flag是通道选择, 用 1~10分别对应开通第1路到第10路串口通道, 图5 是第10路串口所接收的信号局部波形放大图; data_o是并行数据输出; received8位串行数据接 收完毕后, 通过高电平向DSP发出的中断请求信 号, 以便DSP通过读信号read_strobe 读取数据; rxclk_enable是接收串行数据时钟使能; rxclk是接 收串行数据时钟。   从图5的放大图可以看出, 在串口没有接收 数据时, data_o为高阻状态, txclk_enable是低电 平, 因而不使能, txclk没有接收时钟, received 是低电平, 没有置高; 而当开始接收数据时, data_o是高阻态, txclk_enable为高电平使能, txclk 有接收时钟; 此后再当接收完数据时, received 为高电平并向DSP发送中断请求信号; 此 时, DSP响应中断, 并通过read_strobe置低来读 取数据, 从而使数据10出现在并行数据线上。 现在可以从serial10_in结合rxclk来分析接收 到的数据, 串行数据依次是0010100001, 因为第 一位0是起始位, 故数据从第二位算起的八位数 据是01010000, 又因数据是低位先发, 因此, 真 正的数据是00001010 (十进制数是10), 由图中可 以看到, data_o上输出的确实是10。 5 结束语 当一个系统中存在多个异步串行接口时, 基 于ADSP- BF533和CPLD设计的、具有多路UART 接口的系统, 可以方便的分别与多个异步串口进 行通信, 而且灵活性比较强, 成本也很低, 功能 也比较完善。目前, 该设计经实际板子验证, 结 果证明完全可行。 |

/4

/4

用户188034 2009-9-14 19:36