在Cadence allegro中完成布局、布线后,后期还需要进行钻孔、出光绘文件等操作。

本文就钻孔处理步骤进行简要说明。

对于钻孔需要处理的如图中红线标注所示,共有4步,

如果PCB板上还有矩形等非规则的钻孔,则还需要第5步NC Route进行处理。

下面分别说明:

1.Drill Customization

对钻孔的Figure和Characters等进行处理,可以用Auto generate symbols对不同的钻孔产生不同的figure形状,然后再分别对Symbol Characters栏中的钻孔字符进行修改(一般对于不同的钻孔应该对应不同的钻孔字符),最后Validate,OK即可。

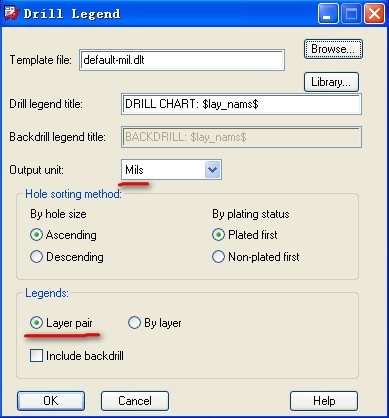

2.Drill Legend

产生钻孔图例,注意单位的选择Mils(与PCB的所有单位设置应一致)。

另外,Legends中有Layer pair和By layer的选择,一般而言,如果板上全为通孔时选择Layer pair;如果板上有盲/埋孔时则选择By layer。

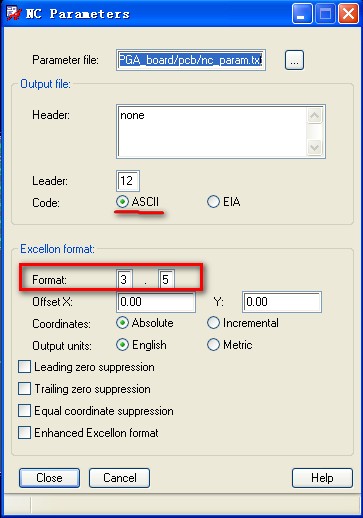

3.NC Parameters设置

Code选择ASCII即可,注意Format的设置,应与出光绘等的格式设置一致,通常精度设为整数3,小数5,如图所示,其他的默认即可。

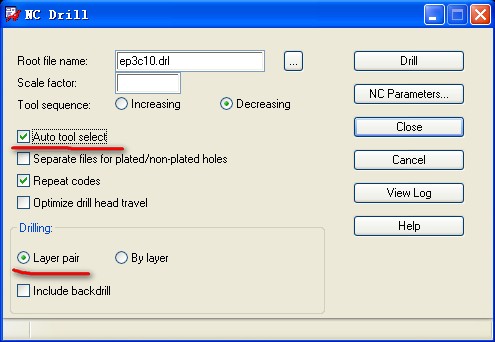

4.NC Drill

这一项的设置通常默认即可,也可以把Auto tool select勾上,这些一般板厂都能处理。

5.NC Route

这一项的设置主要是针对板子上有不规则的钻孔时的处理。

至此,PCB板的钻孔部分的处理就结束了,后续将对出光绘文件的步骤进行说明。

/4

/4

用户1611293 2012-7-19 15:32